无锡泰连芯科技有限公司

## TLX1520 型

14 位 20MSps/40MSps 1.8Z 单通道模数转换器

2024 年 06 月

# 14 位 20MSps/40MSps 1.8V 单通道模数转换器

## 1 主要性能

- **1.8V** 模拟电源供电

- **1.8V-3.3V** 输出供电

- **信噪比(SNR):**

- 75.4dBFS** 在 **9.9MHz** 输入

- 70.5dBFS** 在 **200MHz** 输入

- **三次谐波(HD3):**

- 93dBc** 在 **9.9MHz** 输入

- 80dBc** 在 **200MHz** 输入

- **内置基准电压源, 集成 ADC 输入采样保持**

- **灵活的模拟输入范围: 1Vpp 至 2Vpp**

- **内置时钟占空比稳定器**

- **串行端口控制**

- **多种编码格式:**

- 偏移码、补码、格雷码、随机码

- **可控同步时钟对齐延时**

## 2 应用场合

- **通信**

- **分集无线电系统**

- **多模式数字接收器**

- **GSM、EDGE、W-CDMA、LTE、CDMA2000、WiMAX、TD-SCDMA**

- **I/Q 解调系统**

- **智能天线系统**

- **电池供电仪器**

- **超声设备**

## 3 产品特点

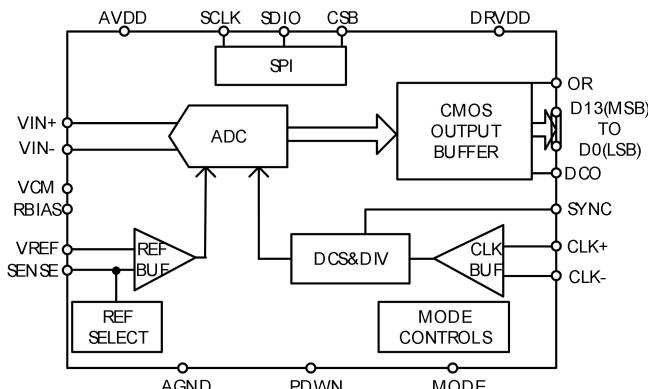

**TLX1520** 模拟单元采用 **1.8V** 单电源供电, 数字输出单元兼容 **1.8V** 至 **3.3V** 供电以支持 **CMOS** 输出。

**TLX1520** 采用专有差分输入电路设计, 在 **200MHz** 的输入频率下仍保持出色的动态性能。

**TLX1520** 配置标准串行接口 (**SPI**), 支持各种标准操作特性和功能控制。

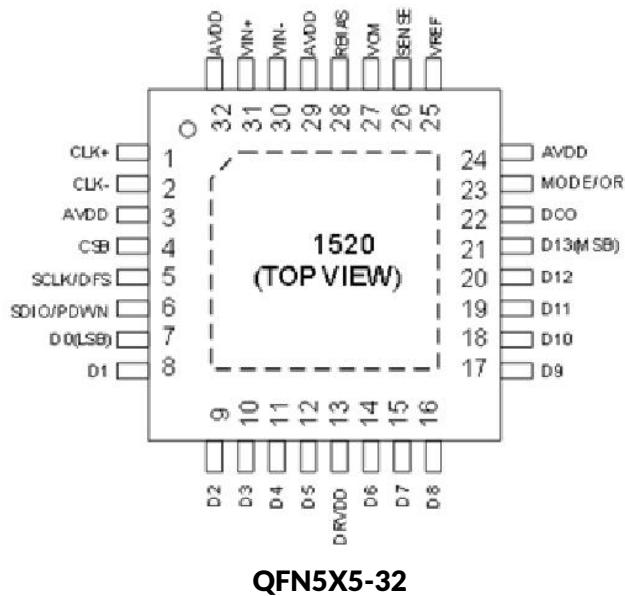

**TLX1520** 采用 **32** 脚 **QFN** 封装, 引脚定义和排列与 **AD9649/29/09** 兼容。

质量等级: 军温级**&N1**级

### 器件信息<sup>(1)</sup>

| 型号      | 封装        | 封装尺寸 (标称值)    |

|---------|-----------|---------------|

| TLX1520 | QFN5X5-32 | 5.00mm×5.00mm |

(1) 详细的订单型号说明, 请参考数据表后的封装选项部分。

图 1. TLX1520系统框图

## 目 录

|                                      |    |

|--------------------------------------|----|

| <b>1 主要性能</b> .....                  | 2  |

| <b>2 应用场合</b> .....                  | 2  |

| <b>3 产品特点</b> .....                  | 2  |

| <b>4 修订历史</b> .....                  | 4  |

| <b>5 封装和订单说明<sup>(1)</sup></b> ..... | 5  |

| <b>6 概述</b> .....                    | 6  |

| <b>7 引脚定义与功能</b> .....               | 7  |

| <b>8 规格参数</b> .....                  | 8  |

| <b>8.1 绝对最大额定参数</b> .....            | 8  |

| <b>8.2 ESD 保护</b> .....              | 8  |

| <b>8.3 热特性</b> .....                 | 8  |

| <b>8.4 ADC 直流特性</b> .....            | 9  |

| <b>8.5 ADC 交流特性</b> .....            | 11 |

| <b>8.6 数字规格</b> .....                | 12 |

| <b>8.7 开关规格</b> .....                | 14 |

| <b>8.8 时序规格</b> .....                | 15 |

| <b>9 时序图</b> .....                   | 15 |

| <b>10 应用电路</b> .....                 | 16 |

| <b>10.1 模拟输入网络</b> .....             | 16 |

| <b>10.2 时钟输入考虑</b> .....             | 16 |

| <b>10.3 基准配置方式</b> .....             | 17 |

| <b>10.4 数字输出</b> .....               | 18 |

| <b>10.5 MODE/OR 模式控制</b> .....       | 19 |

| <b>11 串行端口接口 (SPI)</b> .....         | 20 |

| <b>11.1 使用 SPI 的配置</b> .....         | 20 |

| <b>11.2 不使用 SPI 的配置</b> .....        | 21 |

| <b>12 寄存器地址及默认值:</b> .....           | 22 |

| <b>13 应用与设计</b> .....                | 24 |

| <b>13.1 设计指南</b> .....               | 24 |

| <b>13.2 电源和接地建议</b> .....            | 24 |

| <b>13.3 CMOS 输出驱动力控制</b> .....       | 24 |

| <b>13.4 裸露焊盘散热块建议</b> .....          | 24 |

| <b>13.5 VCM</b> .....                | 24 |

| <b>13.6 RBIAS</b> .....              | 24 |

| <b>13.7 基准电压源去耦</b> .....            | 24 |

| <b>13.8 SPI 端口</b> .....             | 25 |

| <b>14 封装规格尺寸</b> .....               | 26 |

## 4 修订历史

注：以前版本的页码可能与当前版本的页码不同。

| 版本  | 更新日期       | 变更项目 |

|-----|------------|------|

| A.0 | 2024/11/27 | 初始版本 |

## 5 封装和订单说明<sup>(1)</sup>

| 订购型号           | 温度等级            | 封装类型      | 丝印 <sup>(2)</sup> | MSL    | 质量等级   |

|----------------|-----------------|-----------|-------------------|--------|--------|

| JTLX1520YQAH32 | -55 °C ~+125 °C | QFN5X5-32 | TLX1520           | MSL1/3 | N1/军温级 |

| TLX1520YQAH32  | -40 °C ~+125 °C | QFN5X5-32 | TLX1520           | MSL1/3 | 工业级    |

注意:

- (1) 该信息是当前版本的最新数据。这些数据如有更新, 将及时更新到我司官网, 恕不另行通知。

- (2) 丝印可能会有其他附加的代码, 用于产品的内控追溯 (包括数据代码和供应商代码) 或者标志产地。

- (3) **TLXIC** 在我们的装配厂使用符合 **JEDEC** 工业标准 **J-STD-20F** 的通用预处理设置对 **MSL** 级别进行分类。如果您的最终应用对预处理设置非常关键, 或者您有特殊要求, 请与 **TLXIC** 技术支持联系。

## 6 概述

**TLX1520** 是一款单通道、**14** 位模数转换器(**ADC**)，旨在支持需要高性能、低成本、小尺寸且具多功能性的通信应用。这款单通道 **ADC** 内核采用多级、差分流水线架构，并集成了输出纠错逻辑，支持用户采用可外部配置的信号输入电压范围，集成基准电压源可简化设计。**ADC** 数据输出为并行 **CMOS** 标准电平，支持 **1.8 V-3.3V** 供电。**ADC** 的设置与控制都可以采用 **SPI** 兼容型串行接口来完成。**TLX1520** 采用 **32** 引脚 **QFN** 封装，额定工作温度支持**-55°C** 至**+125°C** 的工业级温度范围。

## 7 引脚定义与功能

### 引脚功能

| 引脚 | 引脚名称      | 功能说明               | 引脚 | 引脚名称    | 功能说明          |

|----|-----------|--------------------|----|---------|---------------|

| 1  | CLK+      | 时钟输入正端             | 17 | D9      | 数据输出          |

| 2  | CLK-      | 时钟输入负端             | 18 | D10     | 数据输出          |

| 3  | AVDD      | 模拟模块供电 (1.8V)      | 19 | D11     | 数据输出          |

| 4  | CSB       | spi 片选, 低有效        | 20 | D12     | 数据输出          |

| 5  | SCLK/DFS  | spi 时钟位, 低速数字      | 21 | D13     | 数据输出          |

| 6  | SDIO/PDWN | spi 数据位, 低速数字      | 22 | DCO     | 数据输出同步时钟      |

| 7  | D0        | 数据输出               | 23 | MODE/OR | 模式选择输入端       |

| 8  | D1        | 数据输出               | 24 | AVDD    | 模拟模块供电 (1.8V) |

| 9  | D2        | 数据输出               | 25 | VREF    | 基准电压输入/输出     |

| 10 | D3        | 数据输出               | 26 | SENSE   | 基准电压模式选择      |

| 11 | D4        | 数据输出               | 27 | VCM     | 输入共模偏置        |

| 12 | D5        | 数据输出               | 28 | RBIAS   | 外部基准电阻        |

| 13 | DRVDD     | 数字模块供电 (1.8V-3.3V) | 29 | AVDD    | 模拟模块供电 (1.8V) |

| 14 | D6        | 数据输出               | 30 | VIN-    | 通道输入负端        |

| 15 | D7        | 数据输出               | 31 | VIN+    | 通道输入正端        |

| 16 | D8        | 数据输出               | 32 | AVDD    | 模拟模块供电 (1.8V) |

|    |           |                    | 0  | AGND    | 封装底部裸露焊盘, 接地  |

## 8 规格参数

### 8.1 绝对最大额定参数

| 参数                                                     | 最小值  | 最大值 | 单位       |

|--------------------------------------------------------|------|-----|----------|

| 模拟电源电压 <b>AVDD</b> 至 <b>AGND</b>                       | -0.3 | 2   | <b>V</b> |

| 数字电源电压 <b>DRVDD</b> 至 <b>AGND</b>                      | -0.3 | 3.9 | <b>V</b> |

| 输入电压( <b>VIN+/-, CLK+/-, VREF, SENSE, VCM, RBIAS</b> ) | -0.3 | 2   | <b>V</b> |

| 输入电压( <b>CSB, SCLK/DFS, SDIO/PDWN, MODE/OR</b> )       | -0.3 | 3.9 | <b>V</b> |

| 输出电压( <b>DCO, D0-D13</b> )                             | -0.3 | 3.9 | <b>V</b> |

| 最大结温 <b>T<sub>J,MAX</sub></b>                          |      | 150 | °C       |

| 工作温度范围                                                 | -55  | 125 | °C       |

| 存储温度范围                                                 | -65  | 150 | °C       |

注意，超出上述绝对最大额定值可能会导致器件永久性损坏。这只是额定最值，不表示在这些条件下或者在任何其它超出本技术规范操作章节中所示规格的条件下，器件能够正常工作。长期在绝对最大额定值条件下工作会影响器件的可靠性。

### 8.2 ESD 保护

带电器件和电路板可能会在没有察觉的情况下放电。尽管本产品具有专有保护电路，但在遇到高能量 ESD 时，器件可能会损坏。因此，应当采取适当的 ESD 防范措施，以避免器件性能下降或功能丧失。

### 8.3 热特性

**LFCSP** 封装的裸露焊盘必须焊接到接地层。将裸露焊盘焊接到 **PCB** 上可提高焊接可靠性，从而最大限度发挥封装的热性能。 $\theta_{JA}$  典型值的测试条件为带实接地层的四层 **PCB**，典型值为 **37°C/W**。气流可改善散热，从而降低  $\theta_{JA}$ 。另外，直接与封装引脚接触的金属，包括金属走线、通孔、接地层、电源层，可降低  $\theta_{JA}$ 。

## 8.4 ADC 直流特性

除另有说明, **AVDD=1.8 V**、**DRVDD=1.8 V**、最大采样速率、**VIN=-1.0 dBFS** 差分输入、**1.0 V** 内部基准电压。

| 参数                               | 温度          | 20Msps/40Msps |                  |              | 单位               |

|----------------------------------|-------------|---------------|------------------|--------------|------------------|

|                                  |             | 最小值           | 典型值              | 最大值          |                  |

| 分辨率                              |             |               | <b>14</b>        |              | 位                |

| 精度                               |             |               |                  |              |                  |

| 无失码                              | 全           |               | 保证               |              |                  |

| 失调误差                             | 全           |               | <b>±0.1</b>      | <b>±0.7</b>  | %FSR             |

| 增益误差                             | 全           |               | <b>±0.8</b>      |              | %FSR             |

| 微分非线性 (DNL) <sup>1</sup>         | 全           | <b>-1</b>     |                  | <b>+0.7</b>  | LSB              |

|                                  | <b>25°C</b> |               | <b>±0.45</b>     |              | LSB              |

| 积分非线性 (INL) <sup>1</sup>         | 全           |               |                  | <b>+2</b>    | LSB              |

|                                  | <b>25°C</b> |               | <b>±0.65</b>     |              | LSB              |

| 匹配特性                             |             |               |                  |              |                  |

| 失调误差                             | 全           |               |                  | <b>±0.7</b>  | %FSR             |

| 增益误差                             | 全           |               | <b>±0.2</b>      |              | %FSR             |

| 内部基准电压                           |             |               |                  |              |                  |

| 输出电压误差 (1V 模式)                   | 全           | <b>0.98</b>   |                  | <b>1.005</b> | V                |

| 负载调整率 (1mA)                      | 全           |               | <b>2</b>         |              | mV               |

| 输入端参考噪声, <b>VREF=1V</b>          | <b>25°C</b> |               | <b>0.98</b>      |              | LSBrms           |

| 模拟输入                             |             |               |                  |              |                  |

| 输入范围, <b>VREF=1V</b>             | 全           |               | <b>2</b>         |              | V <sub>p-p</sub> |

| 输入电容 <sup>2</sup>                | 全           |               | <b>6</b>         |              | pF               |

| 输入共模电压                           | 全           |               | <b>0.9</b>       |              | %FSR             |

| 基准电压输入阻抗                         | 全           |               | <b>6</b>         |              | k $\Omega$       |

| 电源/电压电流                          |             |               |                  |              |                  |

| <b>AVDD</b>                      | 全           | <b>1.7</b>    | <b>1.8</b>       | <b>1.9</b>   | V                |

| <b>DRVDD</b>                     | 全           | <b>1.7</b>    |                  | <b>3.6</b>   | V                |

| <b>IAVDD<sup>1</sup></b>         | 全           |               | <b>24.2/35.5</b> |              | mA               |

| <b>IDRVDD (1.8V)<sup>1</sup></b> | 全           |               | <b>1.7/2.8</b>   |              | mA               |

| <b>IDRVDD (3.3V)<sup>1</sup></b> | 全           |               | <b>3.1/5.3</b>   |              | mA               |

| 功耗                               |             |               |                  |              |                  |

| 直流输入                             | 全           |               | <b>45/68</b>     |              | mW               |

| 正弦波输入 (1.8V) <sup>1</sup>        | 全           |               | <b>46.6/68.9</b> |              | mW               |

| 正弦波输入 (3.3V) <sup>1</sup>        | 全           |               | <b>53.8/81.4</b> |              | mW               |

| 待机 <sup>3</sup>                  | 全           |               | <b>15</b>        |              | mW               |

| 掉电                               | 全           |               | <b>0.5</b>       |              | mW               |

---

- (1) 测量条件为：低输入频率、满量程正弦波、每个输出位的负载约为 **5pF**。

- (2) 输入电容指一个差分输入引脚与 **AGND** 之间的有效电容。

- (3) 待机功耗的测量条件为：直流输入、**CLK** 引脚无动作(设为 **AVDD** 或 **AGND**)。

## 8.5 ADC 交流特性

除另有说明, **AVDD=1.8 V**、**DRVDD=1.8 V**、最大采样速率、**VIN=-1.0 dBFS** 差分输入、**1.0 V** 内部基准电压。

| 参数                                           | 温度   | 20MSps/40MSps |      |     | 单位   |

|----------------------------------------------|------|---------------|------|-----|------|

|                                              |      | 最小值           | 典型值  | 最大值 |      |

| 信噪比 (SNR)                                    |      |               |      |     |      |

| $f_{in}=9.9\text{MHz}$                       | 25°C |               | 75.4 |     | dBFS |

| $f_{in}=27\text{MHz}$                        | 25°C |               | 74.7 |     | dBFS |

|                                              | 全    | 73.5          |      |     | dBFS |

| $f_{in}=200\text{MHz}$                       | 25°C |               | 70.5 |     | dBFS |

| 信纳比 (SINR)                                   |      |               |      |     |      |

| $f_{in}=9.9\text{MHz}$                       | 25°C |               | 74.7 |     | dBFS |

| $f_{in}=27\text{MHz}$                        | 25°C |               | 74.0 |     | dBFS |

|                                              | 全    | 73.3          |      |     | dBFS |

| $f_{in}=200\text{MHz}$                       | 25°C |               | 70.0 |     | dBFS |

| 有效位数 (ENOB)                                  |      |               |      |     |      |

| $f_{in}=9.9\text{MHz}$                       | 25°C |               | 12.1 |     | 位    |

| $f_{in}=27\text{MHz}$                        | 25°C |               | 12.0 |     | 位    |

| $f_{in}=200\text{MHz}$                       | 25°C |               | 11.3 |     | 位    |

| 三次谐波                                         |      |               |      |     |      |

| $f_{in}=9.9\text{MHz}$                       | 25°C |               | 93   |     | dBc  |

| $f_{in}=27\text{MHz}$                        | 25°C |               | 84   |     | dBc  |

|                                              | 全    | 80            |      |     | dBc  |

| $f_{in}=200\text{MHz}$                       | 25°C |               | 80   |     | dBc  |

| 无杂散动态范围 (SFDR)                               |      |               |      |     |      |

| $f_{in}=9.9\text{MHz}$                       | 25°C |               | 93   |     | dBc  |

| $f_{in}=27\text{MHz}$                        | 25°C |               | 84   |     | dBc  |

|                                              | 全    | 80            |      |     | dBc  |

| $f_{in}=200\text{MHz}$                       | 25°C |               | 80   |     | dBc  |

| 双音 SFDR, 无扰动                                 |      |               |      |     |      |

| $f_{in}=25.1/27.1\text{MHz} (-7\text{dBFS})$ | 25°C |               | 75   |     | dBc  |

## 8.6 数字规格

除另有说明, **AVDD=1.8V**、**DRVDD=1.8V**、典型采样速率、**VIN=-1.0 dBFS** 差分输入、**1.0V** 内部基准电压。

| 参数                                            | 温度 | 最小值  | 典型值              | 最大值   | 单位               |

|-----------------------------------------------|----|------|------------------|-------|------------------|

| 差分时钟输入 (CLK+/-)                               |    |      |                  |       |                  |

| 逻辑兼容                                          |    |      | CMOS/LVDS/LVPECL |       |                  |

| 内部共模偏置                                        | 全  |      | 0.9              |       | V                |

| 差分输入电压                                        | 全  | 0.3  |                  | 3.6   | V <sub>p-p</sub> |

| 输入电压范围                                        | 全  | AGND |                  | AVDD  | V                |

| 输入共模范围                                        | 全  |      | 0.9              |       | V                |

| 高电平输入电流                                       | 全  | -100 |                  | +100  | μA               |

| 低电平输入电流                                       | 全  | -100 |                  | +100  | μA               |

| 输入电容                                          | 全  |      | 4                |       | pF               |

| 输入电阻                                          | 全  | 8    | 10               | 12    | kΩ               |

| 逻辑输入 (CSB) <sup>4</sup>                       |    |      |                  |       |                  |

| 高电平输入电压                                       |    | 1.2  |                  | DRVDD | V                |

| 低电平输入电压                                       | 全  | AGND |                  | 0.6   | V                |

| 高电平输入电流                                       | 全  | -100 |                  | +100  | μA               |

| 低电平输入电流                                       | 全  | -100 |                  | +100  | μA               |

| 输入电阻                                          | 全  |      | 20               |       | kΩ               |

| 输入电容                                          | 全  |      | 3                |       | pF               |

| 逻辑输入 (SCLK/DFS, MODE, SDIO/PDWN) <sup>5</sup> |    |      |                  |       |                  |

| 高电平输入电压                                       |    | 1.2  |                  | DRVDD | V                |

| 低电平输入电压                                       | 全  | AGND |                  | 0.6   | V                |

| 高电平输入电流                                       | 全  | -100 |                  | +100  | μA               |

| 低电平输入电流                                       | 全  | -100 |                  | +100  | μA               |

| 输入电阻                                          | 全  |      | 20               |       | kΩ               |

| 输入电容                                          | 全  |      | 3                |       | pF               |

| 数字输出                                          |    |      |                  |       |                  |

| <b>DRVDD=1.8V</b>                             |    |      |                  |       |                  |

| 高电平输出电压                                       |    |      |                  |       |                  |

| I <sub>OH</sub> =50 μA                        | 全  | 1.79 |                  |       | V                |

| I <sub>OH</sub> =0.5mA                        | 全  | 1.75 |                  |       | V                |

| 低电平输出电压                                       |    |      |                  |       |                  |

| I <sub>OL</sub> =50 μA                        | 全  |      |                  | 0.05  | V                |

| I <sub>OL</sub> =1.6mA                        | 全  |      |                  | 0.2   | V                |

| <b>DRVDD=3.3V</b>                             |    |      |                  |       |                  |

| 高电平输出电压                                       |    |      |                  |       |                  |

|                   |   |             |  |             |          |

|-------------------|---|-------------|--|-------------|----------|

| $I_{OH}=50 \mu A$ | 全 | <b>3.29</b> |  |             | <b>V</b> |

| $I_{OH}=0.5mA$    | 全 | <b>3.25</b> |  |             | <b>V</b> |

| 低电平输出电压           |   |             |  |             |          |

| $I_{OL}=50 \mu A$ | 全 |             |  | <b>0.05</b> | <b>V</b> |

| $I_{OL}=1.6mA$    | 全 |             |  | <b>0.2</b>  | <b>V</b> |

(4) 内部上拉

(5) 内部下拉

## 8.7 开关规格

除另有说明, **AVDD=1.8 V**、**DRVDD=1.8 V**、典型采样速率、**VIN=-1.0 dBFS** 差分输入、**1.0 V** 内部基准电压。

| 参数                                    | 温度 | 20MSps/40MSps |         |         | 单位     |

|---------------------------------------|----|---------------|---------|---------|--------|

|                                       |    | 最小值           | 典型值     | 最大值     |        |

| 时钟输入参数                                |    |               |         |         |        |

| 输入时钟速率                                | 全  |               |         | 160/320 | MHz    |

| 转换速率                                  | 全  | 3             |         | 20/40   | MSps   |

| 时钟周期, 一分频模式( <b>t<sub>CLK</sub></b> ) |    | 50/25         |         |         | ns     |

| 时钟脉宽高电平( <b>t<sub>OH</sub></b> )      |    |               | 25/12.5 |         | ns     |

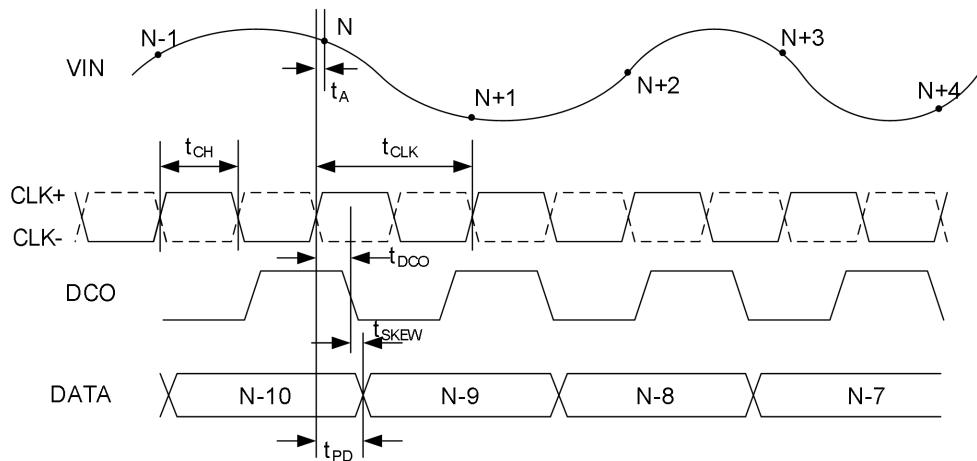

| 孔径延时 ( <b>t<sub>A</sub></b> )         | 全  |               | 1.0     |         | ns     |

| 孔径抖动 ( <b>t<sub>j</sub></b> )         | 全  |               | 0.1     |         | ps rms |

| 数据输出参数                                |    |               |         |         |        |

| 数据传输延迟 ( <b>t<sub>PD</sub></b> )      | 全  |               | 3       |         | ns     |

| DCO 传输延迟 ( <b>t<sub>DCO</sub></b> )   | 全  |               | 5       |         | ns     |

| DCO 至数据偏斜 ( <b>t<sub>SKew</sub></b> ) | 全  | 0.1           | 0.3     | 0.6     | ns     |

| 流水线延迟                                 | 全  |               | 9       |         | 周期     |

| 唤醒时间                                  | 全  |               | 350     |         | μ s    |

| 超范围恢复时间                               | 全  |               | 2       |         | 周期     |

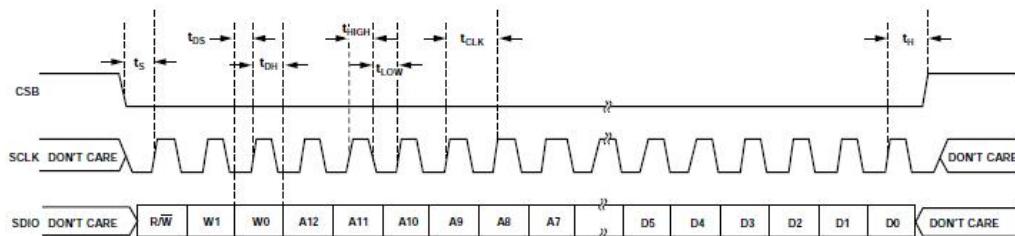

## 8.8 时序规格

| 参数              | 条件                                                  | 最小值 | 典型值 | 最大值 | 单位 |

|-----------------|-----------------------------------------------------|-----|-----|-----|----|

| <b>SPI 时序要求</b> |                                                     |     |     |     |    |

| $t_{DS}$        | 数据与 <b>SCLK</b> 上升沿之间的建立时间                          | 2   |     |     | ns |

| $t_{DH}$        | 数据与 <b>SCLK</b> 上升沿之间的保持时间                          | 2   |     |     | ns |

| $t_{CLK}$       | <b>SCLK</b> 周期                                      | 40  |     |     | ns |

| $t_s$           | <b>CSB</b> 与 <b>SCLK</b> 之间的建立时间                    | 2   |     |     | ns |

| $t_h$           | <b>CSB</b> 与 <b>SCLK</b> 之间的保持时间                    | 2   |     |     | ns |

| $t_{HIGH}$      | <b>SCLK</b> 高电平脉冲宽度                                 | 10  |     |     | ns |

| $t_{LOW}$       | <b>SCLK</b> 低电平脉冲宽度                                 | 10  |     |     | ns |

| $t_{EN\_SDIO}$  | 相对于 <b>SCLK</b> 下降沿, <b>SDIO</b> 引脚从输入状态切换到输出状态所需时间 | 10  |     |     | ns |

| $t_{DIS\_SDIO}$ | 相对于 <b>SCLK</b> 上升沿, <b>SDIO</b> 引脚从输出状态切换到输入状态所需时间 | 10  |     |     | ns |

## 9 时序图

图 2. CMOS 输出数据时序

## 10 应用电路

TLX1520 输入信号、输入时钟、外部直流引脚等外围器件的典型应用电路如下。

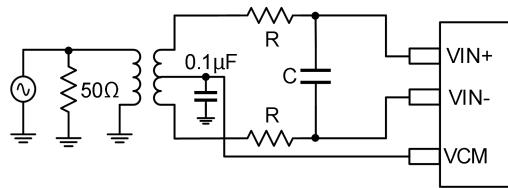

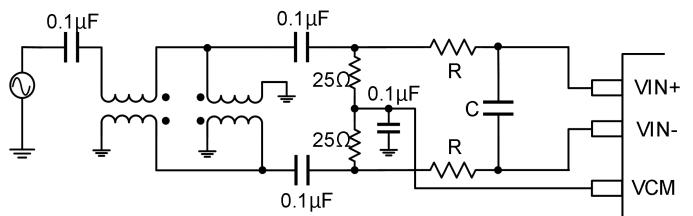

### 10.1 模拟输入网络

在 **SNR** 为关键参数的基带应用中，建议使用的输入配置是差分变压器耦合，如图 3 的示例。为实现模拟输入偏置，须将 **VCM** 电压连接到至变压器次级绕组的中心抽头处。

图 3. 差分变压器耦合配置

在选择变压器时，必需考虑其信号特性。大多数射频变压器在工作频率低于几兆赫兹时，产生饱和现象。信号功率过大也可导致内核饱和，从而导致失真。当输入频率处于第二或更高奈奎斯特区域时，大多数放大器的噪声性能无法满足要求以达到 **ADC** 真正的 **SNR** 性能。在 **SNR** 为关键参数的应用中，建议使用的输入配置是差分双巴伦耦合（见图 4）。在这种配置中，输入交流耦合，**VCM** 通过一个  $25\Omega$  电阻提供给各输入。这些电阻补偿输入巴伦的损耗，向驱动器提供  $50\Omega$  阻抗。

在双巴伦和变压器配置中，输入电容和电阻值取决于输入频率和源阻抗，并且可能需要降低或去掉。表 1 列出了设置 **RC** 网络的建议值。不过这些值取决于输入信号，且只能用作初始参考。

图 4. 差分双巴伦输入配置

表 1. **RC** 网络示例

| 频率范围/MHz | 串联电阻 <b>R</b> /Ω | 差分电容 <b>C</b> /pF |

|----------|------------------|-------------------|

| 0-70     | 33               | 22                |

| 70-200   | 125              | -                 |

### 10.2 时钟输入考虑

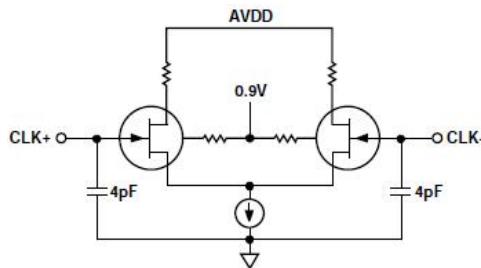

为了充分发挥芯片的性能，应利用一个差分信号作为 **TLX1520** 采样时钟输入端（**CLK+**和 **CLK-**）的时钟信号。通常，应使用一个变压器或两个电容器将该信号交流耦合到 **CLK+**引脚和 **CLK-**引脚内。**CLK+**和 **CLK-**引脚有内部偏置（见图 5），无需外部偏置。如果这些输入悬空，应将 **CLK-**引脚拉低以防止杂散时钟。

图 5. 等效时钟输入电路

TLX1520 的时钟输入结构非常灵活。CMOS、LVDS、LVPECL 或正弦波信号均可作为其时钟输入信号。无论采用哪种信号，都必须考虑到时钟源抖动。

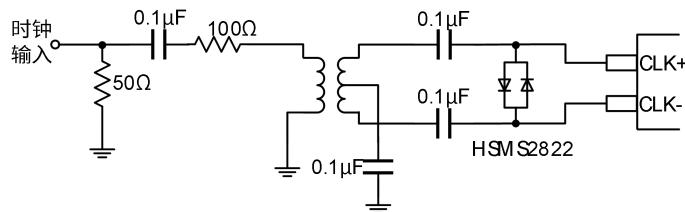

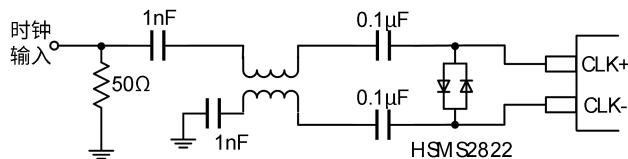

图 6 和图 7 显示两种为 TLX1520 提供时钟信号的首选方法。利用射频巴伦或射频变压器，可将低抖动时钟源的单端信号转换成差分信号。对于超过 100MHz 的时钟频率，可以采样射频巴伦配置；对于 10 MHz 至 200 MHz 的时钟频率，建议采样射频变压器配置。跨接在变压器/巴伦次级上的背对背肖特基二极管可以将输入到 ADC 中的时钟信号限制为约差分 0.8V 峰峰值。这样，既可以防止时钟的大电压摆幅馈通至 ADC 的其它部分，还可以保留信号的快速上升和下降时间，这一点对低抖动性能来说非常重要。

图 6. 变压器耦合差分时钟 (频率可达 200MHz)

图 7. 巴伦耦合差分时钟 (频率可达 8 倍采样率)

### 10.3 基准配置方式

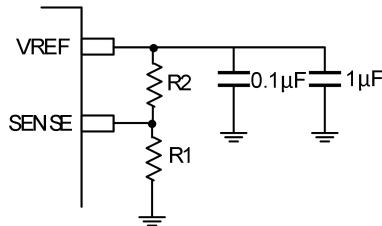

TLX1520 可检测出 SENSE 引脚的电压，从而将基准电压配置成四种不同的模式见表 2。如果 SENSE 引脚接地，则基准放大器开关在内部将 VREF 设为 1.0V（对应 2.0V 峰峰值满量程输入）。在这种模式下，SENSE 接地，也可以通过 SPI 端口调整满量程，详见相应的 SPI 寄存器。将 SENSE 引脚与 VREF 引脚相连，则提供 0.5V 基准输出电压（对应 1V 峰峰值满量程输入）。如果芯片与一个外部电阻分压器相连（如图 8），则使基准放大器进入可编程基准电压模式，VREF 输出端电压的计算公式如下：

$$V_{REF} = 0.5 \times \left( 1 + \frac{R_2}{R_1} \right)$$

无论芯片使用内部基准电压还是外部基准电压, **ADC** 电压输入范围始终是基准电压引脚 (**VREF**) 电压的两倍。

图 8. 可编程基准电压模式

表 2. 基准电压配置汇总

| 所选模式     | SENSE 电压    | 相应的 VREF (V)      | 相应的查分范围 (Vpp) |

|----------|-------------|-------------------|---------------|

| 外部基准电压   | AVDD        | N/A               | 2 × 外部基准电压    |

| 内部固定基准电压 | VREF        | 0.5               | 1.0           |

| 可编程基准电压  | 0.2V 至 VREF | 0.5 × (1 + R2/R1) | 2 × VREF      |

| 内部固定基准电压 | AGND 至 0.2V | 1.0               | 2.0           |

## 10.4 数字输出

**TLX1520** 输出驱动器可以通过改变 **DRVDD** 电源配置为 **1.8V-3.3V CMOS** 逻辑系列接口。在 **CMOS** 输出模式下, 输出驱动器应能够提供足够的输出电流, 以便驱动各种逻辑电路。然而, 大驱动电流可能导致在电源信号中产生毛刺脉冲, 影响转换器的性能。因此在那些需要 **ADC** 来驱动大容性负载或较大扇出的应用中, 可能需要用到外部缓冲器或锁存器。默认输出模式为 **CMOS**, 各通道在单独的总线上输出, 如图 2 所示。

在外部引脚模式下, 设置 **SCLK/DFS** 引脚可以控制数据以偏移二进制格式或二进制补码格式输出(见表 3)。在 **SPI** 控制模式下, 数据的输出格式可选择偏移二进制、二进制补码、格雷码或随机码。

表 3. SCLK、SDIO 外部引脚模式选择

| 引脚电压  | SCLK/DFS   | SDIO/PDWN |

|-------|------------|-----------|

| AGND  | 偏移二进制 (默认) | 正常工作 (默认) |

| DRVDD | 二进制补码      | 芯片掉电模式    |

表 4. 数据输出格式

| 输入 (V)      | 条件               | 偏移二进制模式           | 二进制补码模式           | 超量程 |

|-------------|------------------|-------------------|-------------------|-----|

| VIN+ - VIN- | < -VREF - 0.5LSB | 00 0000 0000 0000 | 10 0000 0000 0000 | 1   |

| VIN+ - VIN- | = -VREF          | 00 0000 0000 0000 | 10 0000 0000 0000 | 0   |

| VIN+ - VIN- | = 0              | 10 0000 0000 0000 | 00 0000 0000 0000 | 0   |

| VIN+ - VIN- | = +VREF - 1LSB   | 11 1111 1111 1111 | 01 1111 1111 1111 | 0   |

| VIN+ - VIN- | > +VREF - 0.5LSB | 11 1111 1111 1111 | 01 1111 1111 1111 | 1   |

## 10.5 MODE/OR 模式控制

在默认情况下，该引脚为溢出指示位，此时寄存器 **0x2A<0>=1**。

进入选项模式，设置寄存器 **0x2A<0>=0** 启用 **MODE** 功能，此时配置寄存器 **0x08<7:5>**会对应不同功能。

## 11 串行端口接口 (SPI)

TLX1520 串行端口接口(SPI)允许用户利用 **ADC** 内部的一个结构化寄存器来配置转换器, 以满足特定功能和操作的需要。**SPI** 具有灵活性, 可根据具体的应用进行定制。通过串行端口, 可访问地址寄存器、对地址寄存器进行读写。存储寄存器以字节为单位进行存储, 并且可以进一步细分成多个区域, 如存储器映射部分所述。

### 11.1 使用 SPI 的配置

该 **ADC** 的 **SPI** 由三部分组成: **SCLK/DFS** 引脚、**SDIO/PDWN** 引脚和 **CSB** 引脚(见表 5)。**SCLK/DFS**(串行时钟)引脚用于同步 **ADC** 的读出和写入数据。**SDIO/PDWN**(串行数据输入/输出)双功能引脚允许将数据发送至内部 **ADC** 存储器映射寄存器或从寄存器中读出数据。**CSB**(片选信号)引脚是低电平有效控制引脚, 它能够使能或者禁用读写周期。

表 5. SCLK、SDIO 外部引脚模式选择

| 引脚          | 功能                                      |

|-------------|-----------------------------------------|

| <b>SCLK</b> | 串行时钟。串行移位时钟输入, 用来同步串行接口                 |

| <b>SDIO</b> | 串行数据输入/出。通常用作输入或输出, 取决于发送的指令和时序帧中的相对位置。 |

| <b>CSB</b>  | 片选信号。低电平有效控制信号, 用来选通读写周期。               |

**CSB** 的下降沿与 **SCLK** 的上升沿共同决定帧的开始。图 9 为串行时序图范例。

**CSB** 可以在多种模式下工作。当 **CSB** 始终维持在低电平状态时, 器件一直处于使能状态; 这称作流。**CSB** 可以在字节之间停留在高电平, 这样可以允许其他外部时序。**CSB** 引脚拉高时, **SPI** 功能处于高阻态模式。在该模式下, 可以开启 **SPI** 引脚的第二功能。在一个指令周期内, 传输一条 16 位指令。在指令传输后将进行数据传输, 数据长度由 **W0** 位和 **W1** 位共同决定。

除了字长, 指令周期还决定串行帧是读操作指令还是写操作指令, 从而通过串行端口对芯片编程或读取片上存储器内的数据。多字节串行数据传输帧的第一个字节的第一位表示发出的是读命令还是写命令。如果指令是回读操作, 则执行回读操作会使串行数据输入/输出(**SDIO**)引脚的数据传输方向, 在串行帧的一定位置由输入改为输出。所有数据均由 8 位字组成。数据可通过 **MSB** 优先模式或 **LSB** 优先模式进行发送。芯片上电后, 默认采用 **MSB** 优先的方式, 可以通过 **SPI** 端口配置寄存器来更改数据发送方式。

图 9. SPI 串行端口接口时序

## 11.2 不使用 SPI 的配置

在不使用 SPI 控制寄存器接口的应用中，**SDIO/PDWN** 引脚、**SCLK/DFS** 引脚用作独立的 **CMOS** 兼容控制引脚。当器件上电后，假设用户希望将这些引脚用作静态控制线，分别控制掉电模式、输出数据格式。在此模式下，**CSB** 片选引脚应与 **DRVDD** 相连，用于禁用串行端口接口。

## 12 寄存器地址及默认值：

除了 **0x00-0x02** 可直接读写外，其他寄存器地址均需通过向地址 **0xFF** 写入 **0x01**，设置传输位，以发出传输命令，否则，向这些地址进行写操作不会影响器件的运行。这样，设置传输位时，就可以在内部同时更新这些寄存器。设置传输位时，进行内部更新，且传输位自动清零。

复位后，将向关键寄存器内载入默认值。表 **6** 寄存器列表内列出了各寄存器的默认值。

表 6. 寄存器列表

| 地址<br><b>A7-0<br/>HEX</b> | 寄存器<br>名称         | 默认<br>值   | 位 7                                                        | 位 6                                      | 位 5                   | 位 4      | 位 3                    | 位 2                                                          | 位 1                                                    | 位 0                                              | 注释                  |

|---------------------------|-------------------|-----------|------------------------------------------------------------|------------------------------------------|-----------------------|----------|------------------------|--------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------|---------------------|

| 芯片配置寄存器                   |                   |           |                                                            |                                          |                       |          |                        |                                                              |                                                        |                                                  |                     |

| <b>0x00</b>               | SPI 端口<br>配置      | <b>18</b> | <b>0</b>                                                   | LSB<br>优先                                | 软复位                   | <b>1</b> | <b>1</b>               | 软复位                                                          | LSB 优<br>先                                             | <b>0</b>                                         | 半字节间<br>镜像          |

| <b>0x01</b>               | 芯片 ID             | <b>6F</b> | 8 位芯片 ID (TLX1520=0x23)                                    |                                          |                       |          |                        |                                                              |                                                        | 只读；                                              |                     |

| <b>0x02</b>               | 芯片<br>等级          |           |                                                            | 速度等级 ID<br>000=20M, 001=40M,<br>010=65M  |                       |          |                        |                                                              |                                                        |                                                  | 只读；器<br>件等级。        |

| 通道索引和传送寄存器                |                   |           |                                                            |                                          |                       |          |                        |                                                              |                                                        |                                                  |                     |

| <b>0xFF</b>               | 传送                | <b>00</b> | <b>0</b>                                                   | <b>0</b>                                 | <b>0</b>              | <b>0</b> | <b>0</b>               | <b>0</b>                                                     | <b>0</b>                                               | 传送                                               | 传送控制                |

| ADC 功能                    |                   |           |                                                            |                                          |                       |          |                        |                                                              |                                                        |                                                  |                     |

| <b>0x08</b>               | 功耗<br>模式          | <b>00</b> | 外部<br>掉电<br>使能                                             | 外部掉电引脚功能<br>00=掉电, 01=待机<br>10=高阻, 11=正常 |                       |          | <b>0</b>               | <b>0</b>                                                     | <b>0</b>                                               | <b>00=正常工作<br/>01=完全掉电<br/>10=待机<br/>11=正常工作</b> | 决定芯片<br>的一般工<br>作模式 |

| <b>0x09</b>               | 全局<br>时钟          | <b>00</b> | <b>0</b>                                                   | <b>0</b>                                 | <b>0</b>              | <b>0</b> | <b>0</b>               | <b>0</b>                                                     | <b>0</b>                                               | 占空比稳定                                            |                     |

| <b>0x0B</b>               | 时钟<br>分频器         | <b>00</b> | <b>0</b>                                                   | <b>0</b>                                 | <b>0</b>              | <b>0</b> | <b>0</b>               | 000=1, 001=2, 010=3,<br>011=4, 100=5, 101=6,<br>110=7, 111=8 |                                                        |                                                  | 时钟分频                |

| <b>0x0E</b>               | <b>BIST</b><br>使能 | <b>00</b> | <b>0</b>                                                   | <b>0</b>                                 | <b>0</b>              | <b>0</b> | <b>0</b>               | <b>0</b>                                                     | <b>0</b>                                               | <b>BIST</b><br>使能                                |                     |

| <b>0x10</b>               | 失调<br>调整          | <b>00</b> | 失调调整以 <b>LSB</b> 为单位，从 <b>+127</b> 到 <b>-128</b> (二进制补码格式) |                                          |                       |          |                        |                                                              |                                                        |                                                  |                     |

| <b>0x14</b>               | 输出<br>模式          | <b>00</b> | <b>0=3.3V<br/>1=1.8V</b>                                   | <b>0</b>                                 | <b>0</b>              | 输出<br>失效 | 输出低<br>功耗              | 输出<br>反相                                                     | <b>00=偏移二进制<br/>01=二进制补码<br/>10=格雷码<br/>11=RAND 编码</b> | 配置输出<br>和数据格<br>式                                |                     |

| <b>0x15</b>               | 输出<br>调整          | <b>22</b> | DCO3V3_<br>drive<1:0>                                      |                                          | DCO1V8_<br>drive<1:0> |          | Data3V3_<br>drive<1:0> |                                                              | Data1V8_<br>drive<1:0>                                 |                                                  | 输出驱动<br>力调整         |

|      |         |    |                                                                  |   |   |   |   |                                                                                 |   |                |               |

|------|---------|----|------------------------------------------------------------------|---|---|---|---|---------------------------------------------------------------------------------|---|----------------|---------------|

| 0x16 | 时钟相位控制  | 00 | DCO 反相                                                           | 0 | 0 | 0 | 0 | 000=无延迟,<br>001=1, 002=2, 003=3,<br>004=4, 005=5, 006=6,<br>007=7, 008=8 输入时钟周期 |   |                |               |

| 0x17 | DCO 延迟  | 00 | 0                                                                | 0 | 0 |   | 0 | 延时=0.56ns*寄存器值<2:0>                                                             |   |                |               |

| 0x18 | 参考选取    | 80 | 100=2Vpp (默认)<br>011=1.6Vpp, 010=1.33Vpp<br>001=1.14Vpp, 00=1Vpp |   |   | 0 | 0 | 0                                                                               | 0 | 0              | 参考电压选择, 影响满量程 |

| 0x2A | OR/MODE | 01 | 0                                                                | 0 | 0 | 0 | 0 | 0                                                                               | 0 | 0=MODE<br>1=OR | 23号引脚功能选择     |

## 13 应用与设计

### 13.1 设计指南

在进行 **TLX1520** 的系统设计和布局之前，建议设计者先熟悉下述设计指南，其中讨论了某些引脚所需的特殊电路连接和布局布线要求。

### 13.2 电源和接地建议

建议使用两个独立的 **1.8 V** 电源为 **TLX1520** 供电：一个用于模拟端(**AVDD**)，一个用于数字输出端(**DRVDD**)。对于 **AVDD** 和 **DRVDD**，应使用多个不同的去耦电容以支持高频和低频。去耦电容应放置在接近 **PCB** 入口点和接近器件引脚的位置，并尽可能缩短走线长度。**TLX1520** 仅需要一个 **PCB** 接地层。对 **PCB** 模拟、数字和时钟模块进行合理的去耦和巧妙的分隔，可以轻松获得最佳的性能。

### 13.3 CMOS 输出驱动力控制

上电时，**TLX1520** 默认采用 **CMOS** 输出驱动。通过 **0x14<7>** 和 **0x15** 寄存器配合，可以控制不同 **DRVDD** 条件下的输出驱动力，驱动力越大，动态功耗也会越大。在低速模式下（例如采样速度低于 **20MSps**），通过 **0x14<3>** 可以将输出驱动力进一步降低至低功耗驱动模式。不论驱动力配置情况，都需要注意同步时钟 **DCO** 与 **ADC** 输出数据间的相位和时序关系，以确保能准确获取 **14** 位的 **ADC** 量化结果。

### 13.4 裸露焊盘散热块建议

为获得最佳的电气性能和热性能，必须将 **ADC** 底部的裸露焊盘连接至模拟地(**AGND**)。**PCB** 上裸露(无阻焊膜)的连续铜平面应与 **TLX1520** 的裸露焊盘(引脚 **0**)匹配。铜平面上应有多个通孔，以便获得尽可能低的热阻路径以通过 **PCB** 底部进行散热。应当填充或堵塞这些通孔，防止通孔渗锡而影响连接性能。

为了最大化地实现 **ADC** 与 **PCB** 之间的覆盖与连接，应在 **PCB** 上覆盖一个丝印层，以便将 **PCB** 上的连续平面划分为多个均等的部分。这样，在回流焊过程中，可在 **ADC** 与 **PCB** 之间提供多个连接点。而一个连续的、无分割的平面则仅可保证在 **ADC** 与 **PCB** 之间有一个连接点。

### 13.5 VCM

**VCM** 引脚应通过一个 **0.1  $\mu$  F** 电容去耦至地。

### 13.6 RBIAS

**TLX1520** 要求用户将一 **10 k $\Omega$**  电阻置于 **RBIAS** 引脚与地之间。该电阻用来设置 **ADC** 内核的主基准电流，该电阻容差至少为 **1%**。

### 13.7 基准电压源去耦

**VREF** 引脚应通过外部一个低 **ESR 0.1  $\mu$  F** 陶瓷电容和一个低 **ESR 1.0  $\mu$  F** 电容的并联去耦至地。

### 13.8 SPI 端口

当需要转换器充分发挥其全动态性能时，应禁用 **SPI** 端口。通常 **SCLK** 信号、**CSB** 信号和 **SDIO** 信号与 **ADC** 时钟是异步的，因此，这些信号中的噪声会降低转换器性能。如果其它器件使用板上 **SPI** 总线，则可能需要在该总线与 **TLX1520** 之间连接缓冲器，以防止这些信号在关键的采样周期内，在转换器的输入端发生变化。

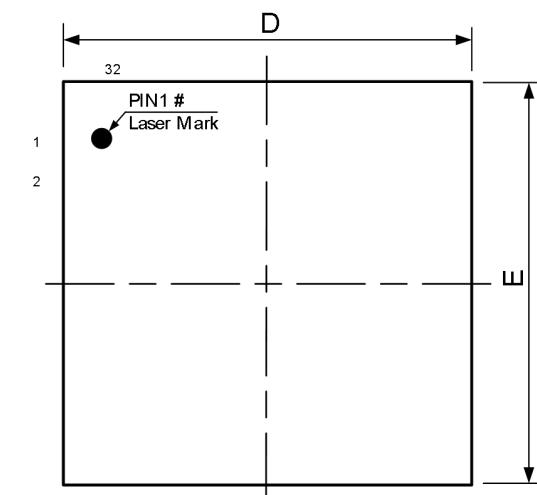

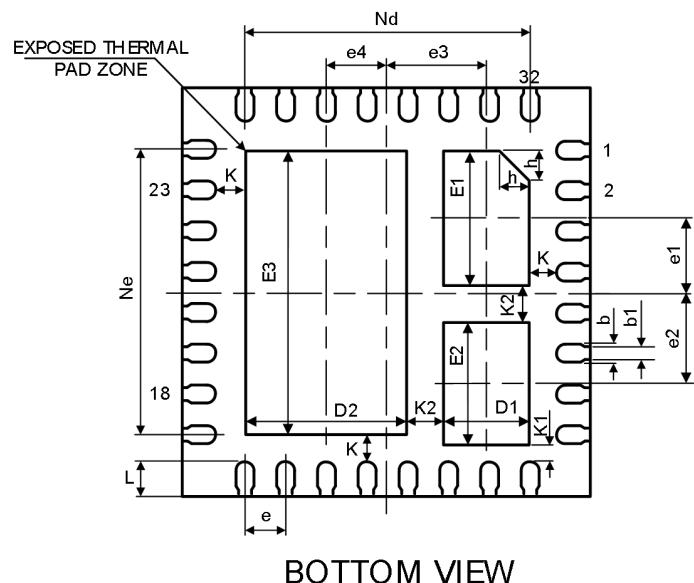

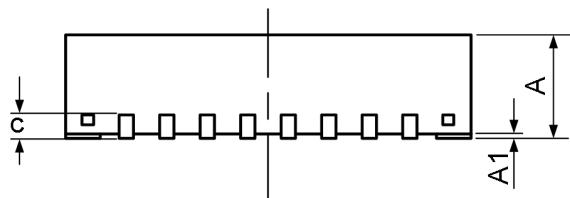

## 14 封装规格尺寸

QFN5X5-32<sup>(4)</sup>

TOP VIEW

BOTTOM VIEW

SIDE VIEW

| Symbol           | Dimensions In Millimeters |       | Dimensions In Inches     |       |

|------------------|---------------------------|-------|--------------------------|-------|

|                  | Min                       | Max   | Min                      | Max   |

| A <sup>(1)</sup> | 0.800                     | 0.900 | 0.032                    | 0.035 |

| A1               | 0.000                     | 0.050 | 0.000                    | 0.002 |

| c                | 0.203 REF <sup>(2)</sup>  |       | 0.008 REF <sup>(2)</sup> |       |

| b                | 0.200                     | 0.300 | 0.008                    | 0.012 |

| b1               | 0.180 REF <sup>(2)</sup>  |       | 0.008 REF <sup>(2)</sup> |       |

| D <sup>(1)</sup> | 4.900                     | 5.100 | 0.193                    | 0.201 |

| D1               | 0.950                     | 1.150 | 0.037                    | 0.045 |

| D2               | 1.870                     | 2.070 | 0.074                    | 0.082 |

| e                | 0.500 BSC <sup>(3)</sup>  |       | 0.020 BSC <sup>(3)</sup> |       |

| e1               | 0.910 BSC <sup>(3)</sup>  |       | 0.036 BSC <sup>(3)</sup> |       |

| e2               | 1.125 BSC <sup>(3)</sup>  |       | 0.044 BSC <sup>(3)</sup> |       |

| e3               | 1.215 BSC <sup>(3)</sup>  |       | 0.048 BSC <sup>(3)</sup> |       |

| e4               | 0.752 BSC <sup>(3)</sup>  |       | 0.030 BSC <sup>(3)</sup> |       |

| Nd               | 3.500 BSC <sup>(3)</sup>  |       | 0.138 BSC <sup>(3)</sup> |       |

| Ne               | 3.500 BSC <sup>(3)</sup>  |       | 0.138 BSC <sup>(3)</sup> |       |

| E <sup>(1)</sup> | 4.900                     | 5.100 | 0.193                    | 0.201 |

| E1               | 1.560                     | 1.760 | 0.061                    | 0.069 |

| E2               | 1.390                     | 1.590 | 0.055                    | 0.063 |

| E3               | 3.380                     | 3.580 | 0.133                    | 0.141 |

| L                | 0.350                     | 0.450 | 0.014                    | 0.018 |

| h                | 0.300                     | 0.400 | 0.012                    | 0.016 |

| K                | 0.360 REF <sup>(2)</sup>  |       | 0.014 REF <sup>(2)</sup> |       |

| K1               | 0.230 REF <sup>(2)</sup>  |       | 0.009 REF <sup>(2)</sup> |       |

| K2               | 0.460 REF <sup>(2)</sup>  |       | 0.018 REF <sup>(2)</sup> |       |

注意：

1. 不包括每边最大 0.075 毫米的塑料或金属突起。

2. REF 是 Reference 的缩写。

3. BSC(中心之间的基本间距)，“基本”间距是标称的。

4. 此图纸如有更改，恕不另行通知。