无锡泰连芯科技有限公司

**TLX48LCM1616型**

**256Mb SDRAM同步动态随机存储器**

2024年06月

## 版本记录

| 版本    | 日期         | 描述                                 |

|-------|------------|------------------------------------|

| V1.00 | 2022年6月29日 | 第一版                                |

| V1.01 | 2023年9月26日 | 1. 更新电参数                           |

| V1.02 | 2023年12月7日 | 1. 添加器件重量, 焊装工艺, 焊盘推荐, 器件标识, 多质量等级 |

| V1.03 | 2024年9月3日  | 1. 更改手册描述内容                        |

|       |            |                                    |

|       |            |                                    |

|       |            |                                    |

## 目录

|                       |    |

|-----------------------|----|

| 1 产品概述                | 2  |

| 1.1 主要特点              | 2  |

| 1.2 功能描述              | 2  |

| 1.3 引脚排布              | 3  |

| A0-A12                | 3  |

| 1.4 原理框图              | 4  |

| 2 器件说明                | 5  |

| 2.1 真值表               | 5  |

| 2.2 功能说明              | 5  |

| 2.2.1. 模式寄存器          | 5  |

| 2.2.2. 初始化            | 7  |

| 2.2.3. 激活操作           | 7  |

| 2.2.4. 读取操作           | 8  |

| 2.2.5. 写入操作           | 8  |

| 2.2.6. 预充电            | 9  |

| 2.2.7. 自动刷新           | 9  |

| 2.2.8. 自刷新            | 10 |

| 2.2.9. Power-Down     | 11 |

| 2.2.10. 时序图           | 12 |

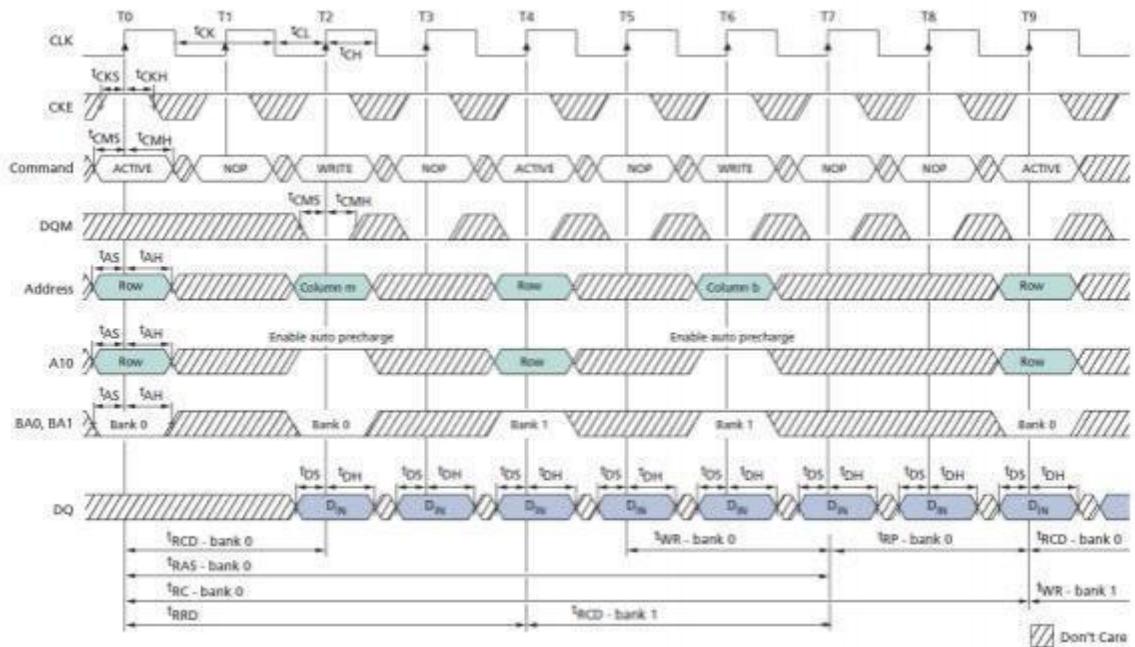

| 图 2-17 交替 BANK 写入操作时序 | 16 |

| 3 电特性                 | 17 |

| 3.1 绝对最大额定值           | 17 |

| 3.2 推荐工作条件            | 17 |

| 3.3 直流 (DC) 特性表       | 18 |

| 3.4 交流 (AC) 特性表       | 18 |

| 4 说明事项                | 20 |

| 4.1 运输与储存             | 20 |

| 4.2 开箱与检查             | 20 |

| 4.3 使用操作规程及注意事项       | 20 |

| 4.4 质量保证              | 20 |

| 5 封装尺寸                | 21 |

| 5.1 TSOP54 外形尺寸图      | 21 |

| 5.2 器件重量              | 22 |

| 5.3 推荐焊装工艺            | 22 |

| 5.4 推荐焊盘尺寸            | 23 |

| 6 订货信息                | 24 |

| 6.1 选型列表              | 24 |

# 1 产品概述

## 1.1 主要特点

- 工作电压: VDD=3.3V±0.3V , VDDQ=3.3V±0.3V

- 存储容量: 256Mbit

- 存储结构: 16Mb×16(4Mb×16×4banks)

- 时钟频率: 133MHz

- 兼容PC100和PC133标准

- 完全同步: 所有信号在系统时钟上升沿锁存

- 可编程的CAS延迟(CAS Latency): 2 、 3

- 可编程突发长度(Burst Lengths): 1 、 2 、 4 、 8或全页面

- 自刷新和自动刷新模式

- 兼容LVTTL电平标准

- 封装形式: TSOP54

- 湿度敏感等级: 3级

- ESD 等级: 2 级(2000V)

- 温度范围: -55°C ~ +125°C

- 质量等级: 军温级&N1级

## 1.2 功能描述

TLX48LCM1616 型256Mb 同步动态随机存储器, 是一款高速 CMOS 电路, 符合行业同类产品 的标准。

TLX48LCM1616 型 256Mb 同步动态随机存储器采用4 个bank 结构, 每个bank 大小为 4Mbit × 16 。 电路所有的控制信号、地址信号、数据信号与 电路外部提供的时钟 CLK 同步, 各信号的逻辑状态都需要通过 CLK 的上升沿采样确定。 电路的各操作指令序列 与 MT48LC16M16A2TG-75 兼容。

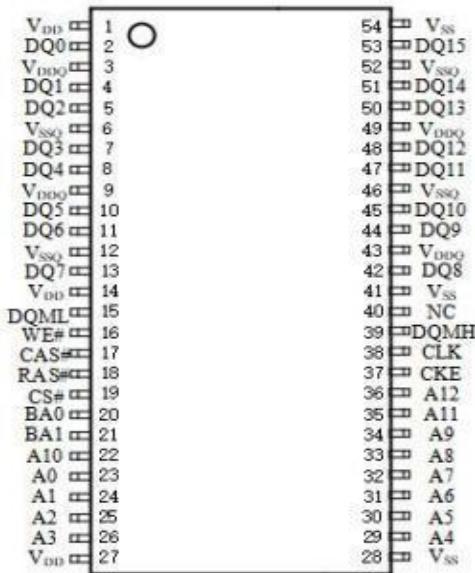

### 1.3 引脚分布

图 1-1 引出端排列 (顶视图)

表 1-1 管脚定义

| 符号            | 类型 | 功能描述                                                                                                  |

|---------------|----|-------------------------------------------------------------------------------------------------------|

| CLK           | 输入 | 时钟信号：<br>所有 SDRAM 的输入信号在时钟 CLK 的上升沿进行采样                                                               |

| CKE           | 输入 | 时钟使能：<br>CKE 为高时，使能时钟正常工作；<br>CKE 为低时，使能 Power-down 模式或自刷新功能。                                         |

| CS#           | 输入 | 芯片选择使能：<br>CS#为高时，芯片不使能，屏蔽外部所有命令； CS#为低时，使能芯片选择，响应外部命令。                                               |

| RAS#、CAS#、WE# | 输入 | 命令输入：<br>RAS#、CAS#、WE#定义 SDRAM 芯片的操作命令。                                                               |

| DQML、DQMH     | 输入 | 数据掩码信号：<br>当进行写入操作时，DQM 是一个输入掩码信号； 当进行读取操作时，DQM 是一个输出使能 信号。<br>DQM为低时有效，DQML控制DQ0~DQ7，DQMH控制DQ8~DQ15。 |

| BA0、BA1       | 输入 | BANK地址输入：<br>BA0和BA1定义在激活、读取、写入或预充电命令时操作的 BANK。                                                       |

| A0-A12        | 输入 | 地址输入：                                                                                                 |

| 符号       | 类型  | 功能描述                                                                                                                                                                                                                                                                                                                                                    |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |     | <p>在激活命令的时候提供 Row地址；<br/>     在读取/写入命令的时候提供 Column 地址；<br/>     在预充电命令时提供 A10 地址： A10 为高时对所有bank 进行预充 电， A10 为低时对BA0 ， BA1 选择的bank 进行预充电；<br/>     在加载模式寄存器命令的时候提供 op-code。</p> <p>Row地址： A0-A12<br/>     Column地址： A0-A8</p> <p>注：该产品手册标注容量为 16Mb<sub>x</sub>16, 但实际采用32Mb<sub>x</sub>16的晶圆封装，因此在实际使用时，软件上要对列地址A9进行拉高或拉低配置，避免A9处于不定态时数据存储到其他地址空间上。</p> |

| DQ0-DQ15 | I/O | 数据总线                                                                                                                                                                                                                                                                                                                                                    |

| VDD      | 电源  | 供电电源： 3.3V±0.3V                                                                                                                                                                                                                                                                                                                                         |

| VDDQ     | 电源  | DQ 供电电源： 3.3V±0.3V                                                                                                                                                                                                                                                                                                                                      |

| VSS      | 地   | 地                                                                                                                                                                                                                                                                                                                                                       |

| VSSQ     | 地   | DQ 地                                                                                                                                                                                                                                                                                                                                                    |

|          |     | 注：该产品手册标注容量为 16Mb <sub>x</sub> 16, 但实际采用32Mb <sub>x</sub> 16的晶圆封装，因此在实际使用时，软件上要对列地址A9进行拉高或拉低配置，避免A9处于不定态时数据存储到其他地址空间上。                                                                                                                                                                                                                                  |

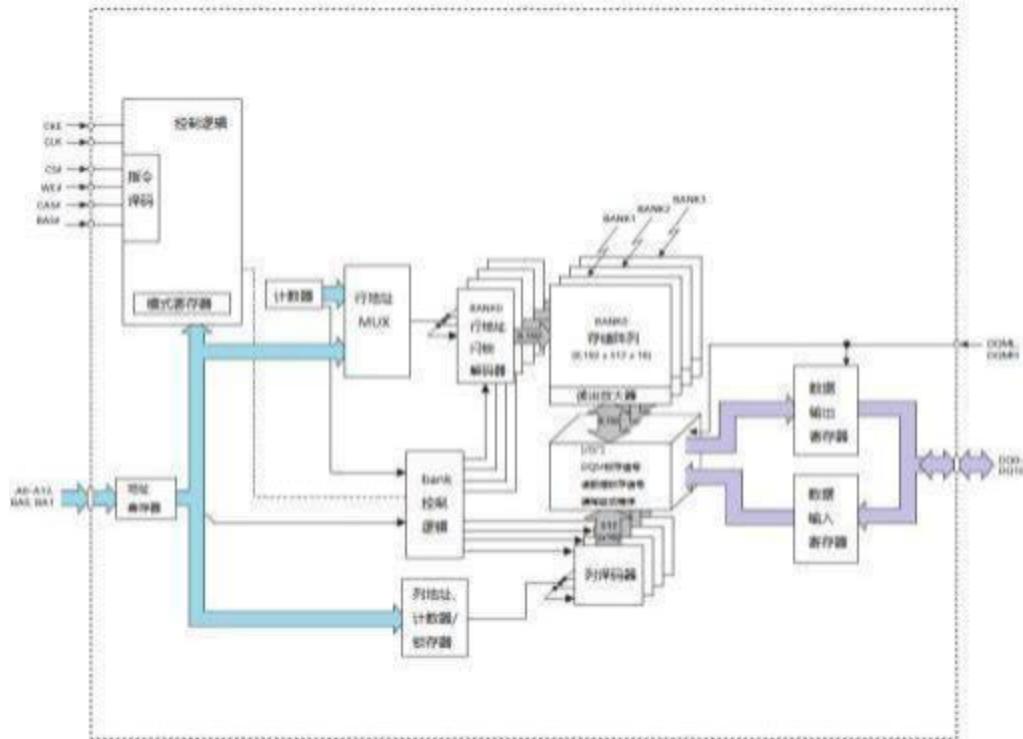

## 1.4 原理框图

图 1-2 TLX48LCM1616 功能原理图

## 2 器件说明

### 2.1 真值表

表 2-1 描述的是 SDRAM 的命令真值表，可对应查询。

表 2-1 SDRAM 命令真值表

| 功能                            | CS# | RAS# | CAS# | WE# | DQM | ADDR     | DQs    |

|-------------------------------|-----|------|------|-----|-----|----------|--------|

| 命令禁止(NOP)                     | H   | X    | X    | X   | X   | X        | X      |

| 不操作(NOP)                      | L   | H    | H    | H   | X   | X        | X      |

| 激活(选择BANK 和激活 Row)            | L   | L    | H    | H   | X   | Bank/Row | X      |

| 读取操作(选择 BANK 和 Column，开始突发读取) | L   | H    | L    | H   | L/H | Bank/Col | X      |

| 写入操作(选择 BANK 和 Column，开始突发写入) | L   | H    | L    | L   | L/H | Bank/Col | Valid  |

| 突发终止                          | L   | H    | H    | L   | X   | X        | ACTIVE |

| 预充电操作(关闭激活的 Row 和 BANK)       | L   | L    | H    | L   | X   | Code     | X      |

| 自动刷新或自刷新                      | L   | L    | L    | H   | X   | X        | X      |

| 加载模式寄存器                       | L   | L    | L    | L   | X   | Op-Code  | X      |

| 写入使能/输出使能                     | --  | --   | --   | --  | L   | --       | ACTIVE |

| 写入禁止/输出高阻                     | --  | --   | --   | --  | H   | --       | High-Z |

### 2.2 功能说明

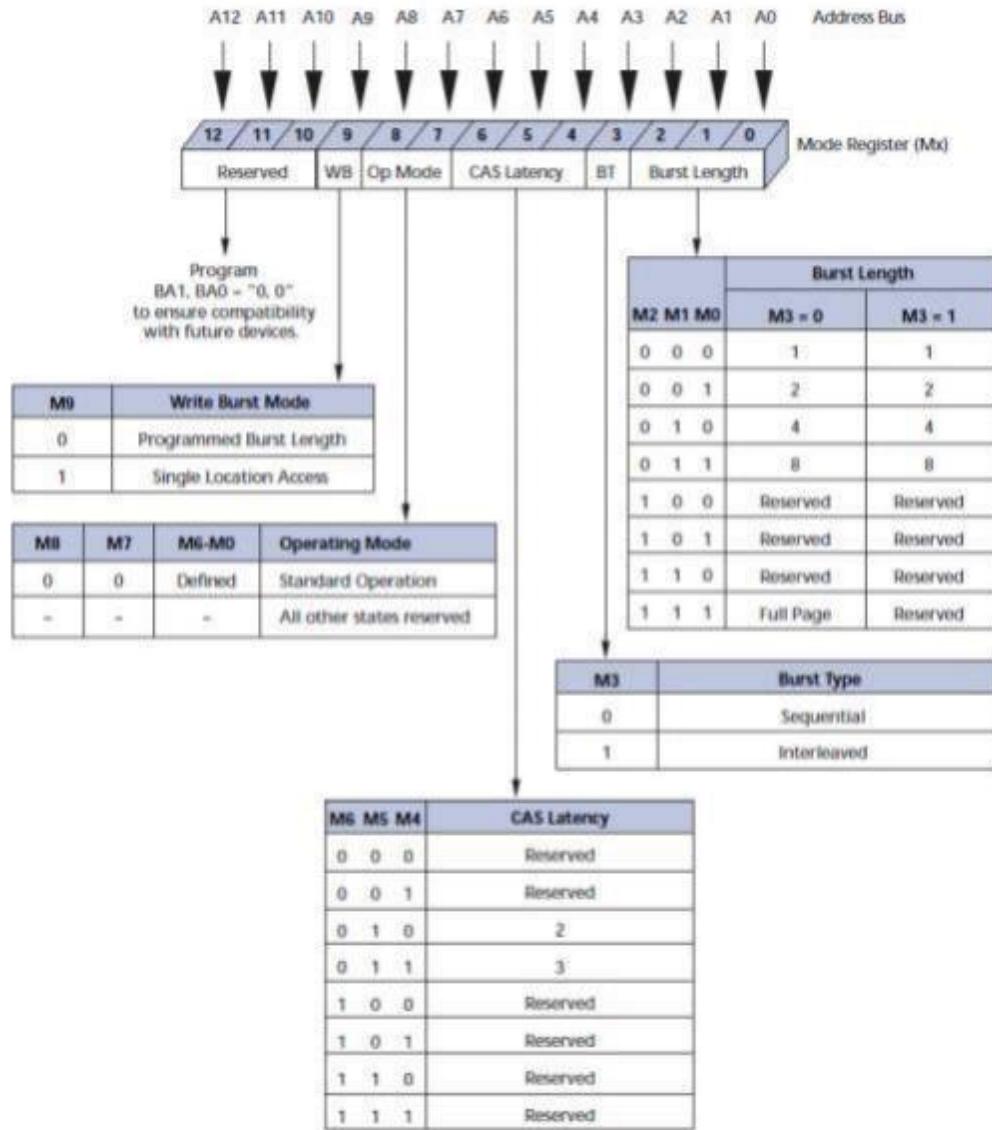

#### 2.2.1. 模式寄存器

模式寄存器用来定义 SDRAM 的操作模式，包括突发长度(Burst Length)、突发类型(Burst Type)、CAS 延迟(CAS Latency)、操作模式和突发写模式。如图 2-1 所示。模式寄存器通过加载模式寄存器(LMR)命令来进行设置，并且 SDRAM 会保存所设置的信息直到其被重新设置或芯片掉电。

图 2-1 模式寄存器定义

① Burst Length (BL): 突发长度。SDRAM 的读写操作都是突发类型的，突发长度决定了在读操作或写操作中列空间存储数据或访问数据的最大个数，可根据要求设置为 1、2、4、8 或全页面。

② Burst Type: 突发类型。突发类型分为 sequential 或 interleaved。由 M3 决定。

③ CAS Latency (CL): 列地址选通脉冲时间延迟。指在读取数据时，需要等待的时钟周期数，可设置为 2 或 3。

④ Operating Mode: 正常操作模式，其他操作模式未定义。

⑤ Write Burst Mode: 突发写模式选择，一种是和读取命令一样，利用BL来设置突发写模式，另一种是单独的写入操作，单地址存取(非突发)。

⑥ BA1 和 BA0 在进行模式寄存器配置时，必须均置为“0”，即  $BA<1:0>=2'b00$  才能进行模式寄存器配置，否则模式寄存器就不能被配置，这时候的 MRS 指令就是一个无效的指令，芯片内部的模式寄存器不会被改写。

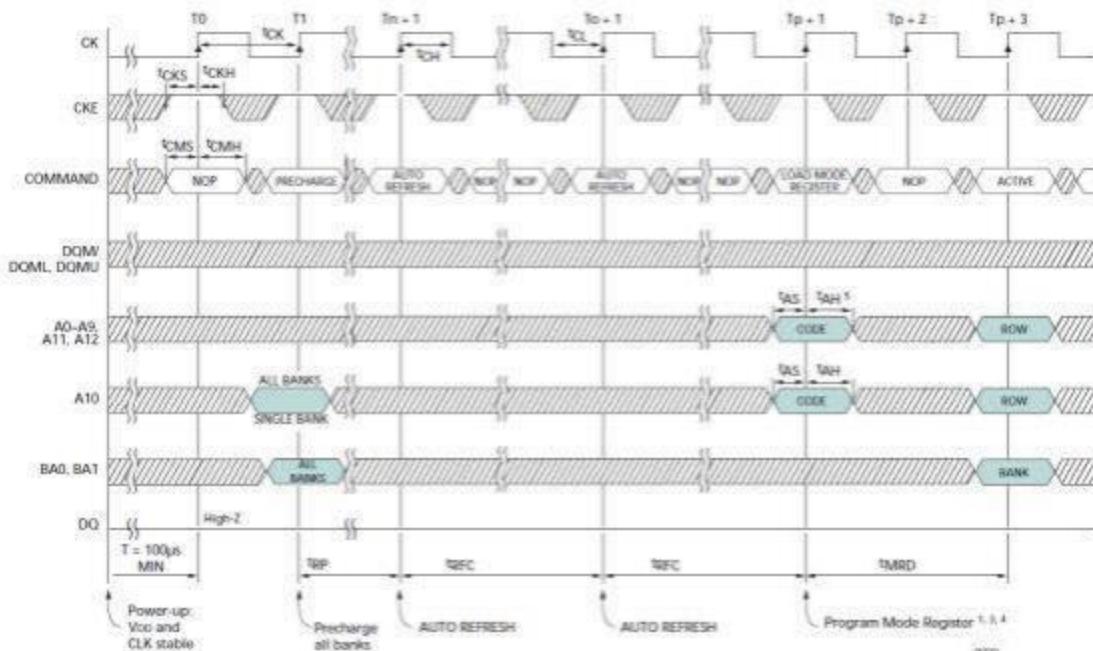

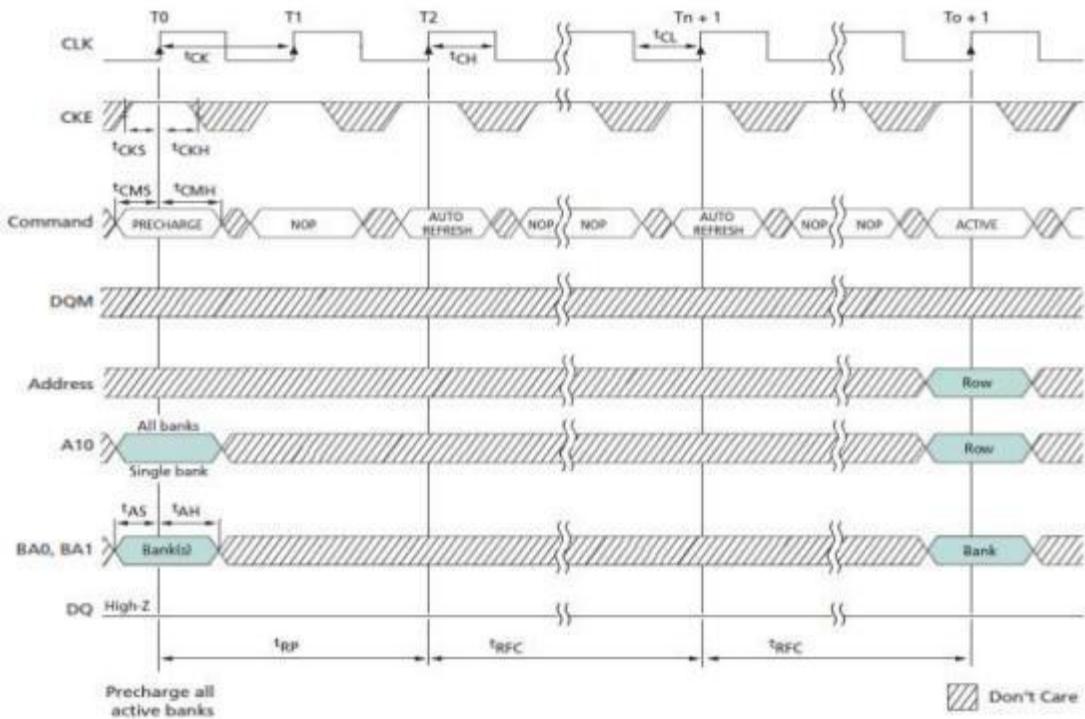

## 2.2.2. 初始化

SDRAM 芯片在上电后必须经过初始化后才能进行读写操作，其初始化时序如图 2-2 所示。在上电稳定后，保持时钟输入，CKE 使能，等待 100us 延时后，开始 NOP 操作，然后后续经过预充电命令(PRECHARGE)，等待 tRP 延时后，进行两次自动刷新(Auto Refresh)后，等待 tRFC 延时后，利用 LMR 命令进行模式寄存器的设置，等待 tMRD 延时后，SDRAM 完成初始化工作，可以进行读写操作。

图 2-2 SDRAM 初始化时序

## 2.2.3. 激活操作

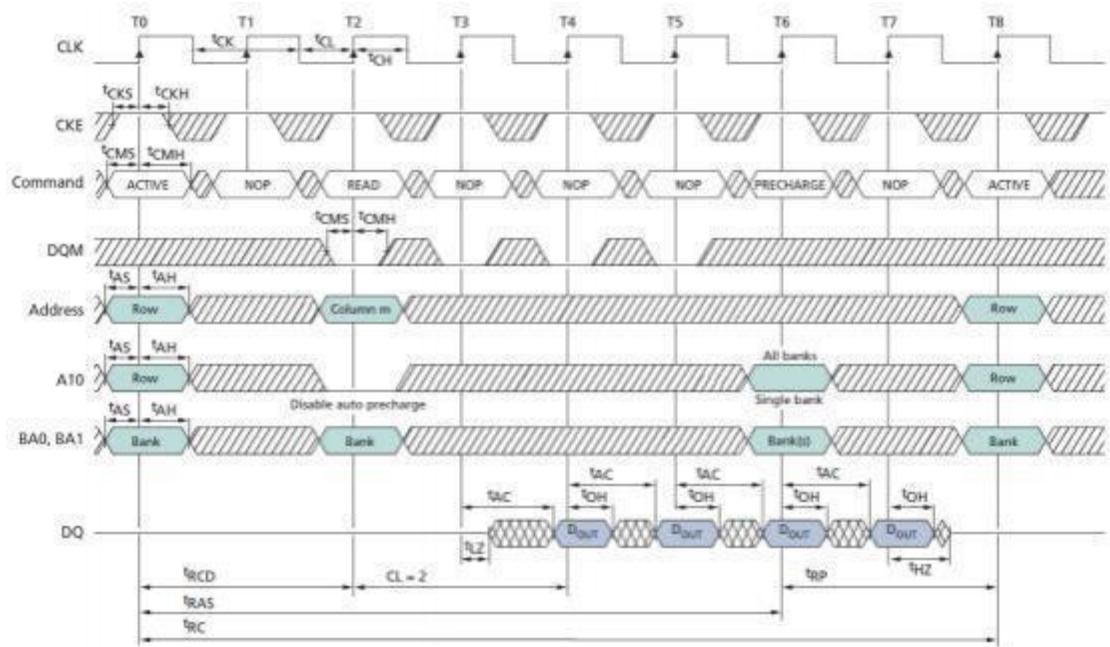

激活操作(ACTIVE)是指在读取或者写入操作之前，芯片需要将要操作的 Bank 和 Row 进行激活，方便后续的操作，命令时序如图 2-3 所示。激活操作是通过激活命令实现的，在激活命令经过时间 tRCD 后，可以进行读取或写入操作。

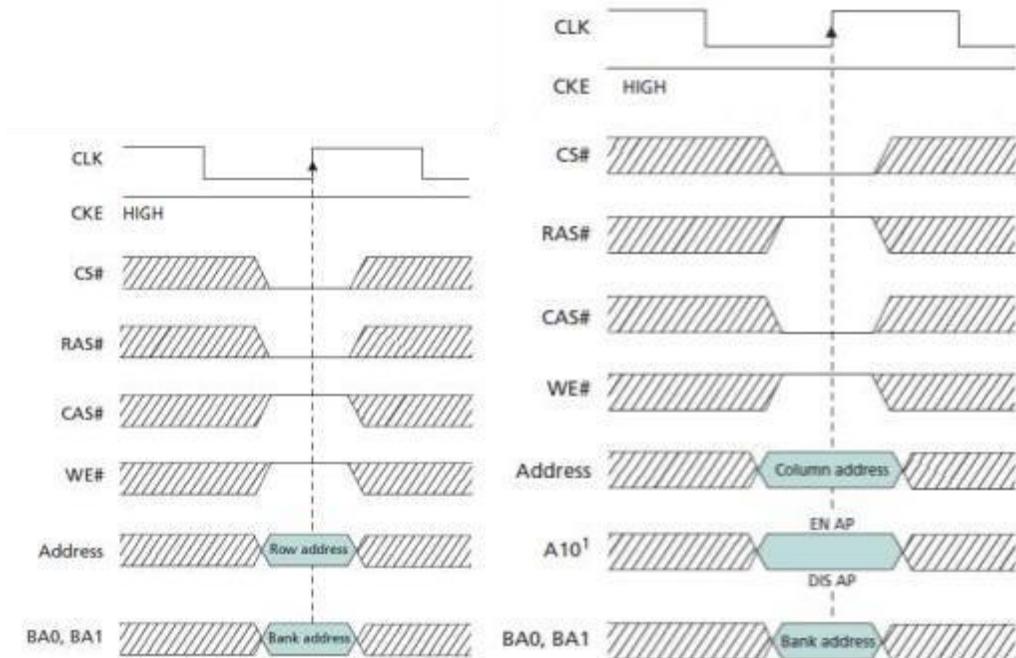

图 2-3 激活命令时序

图 2-4 读取命令时序

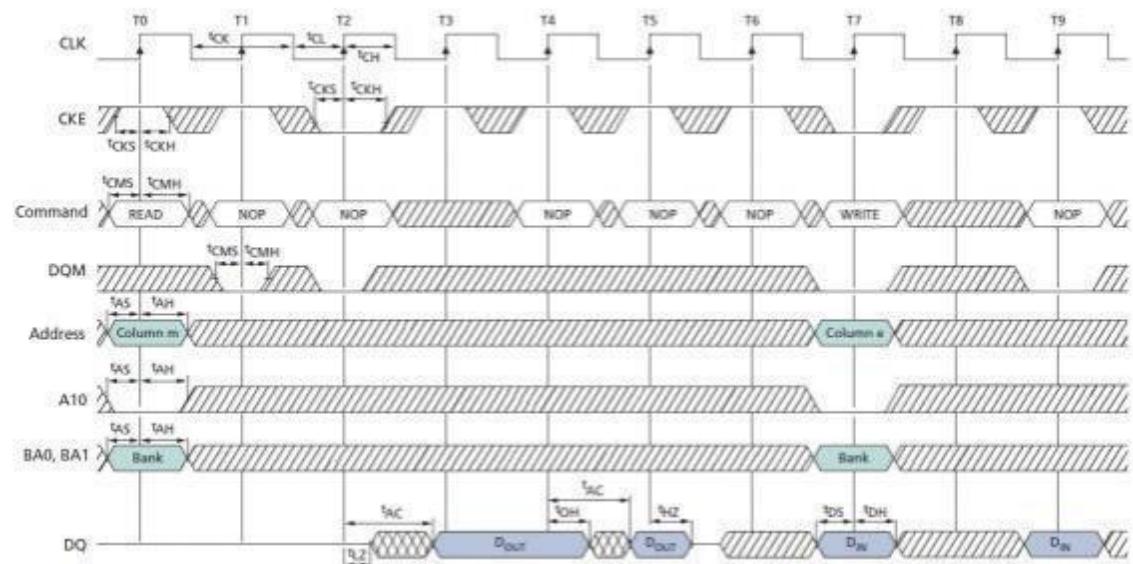

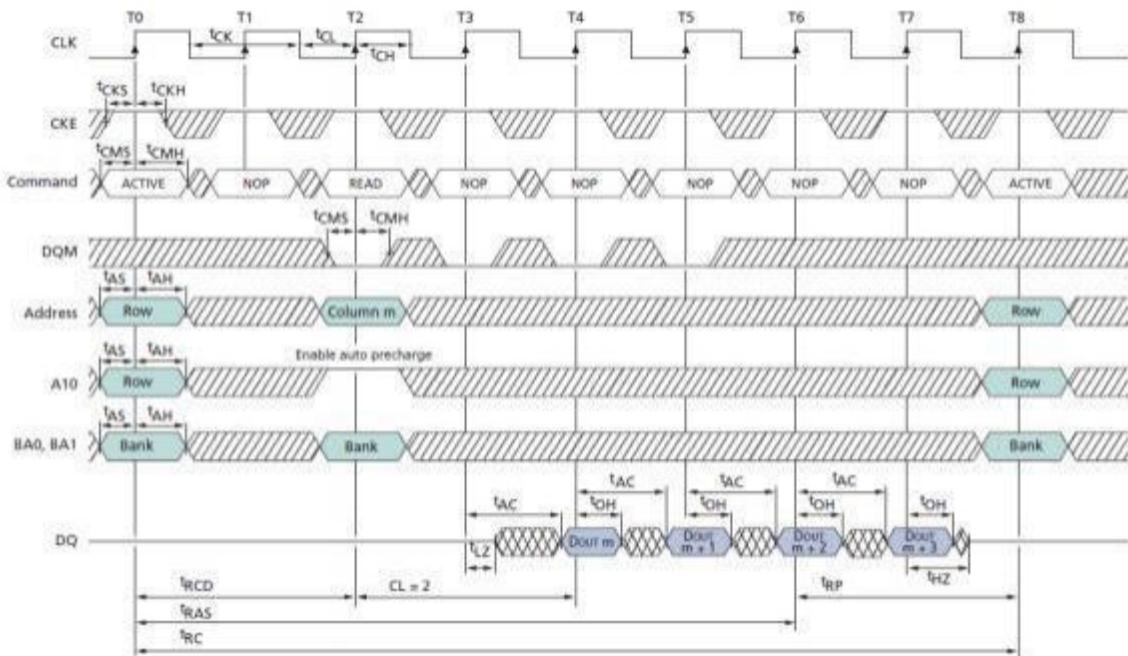

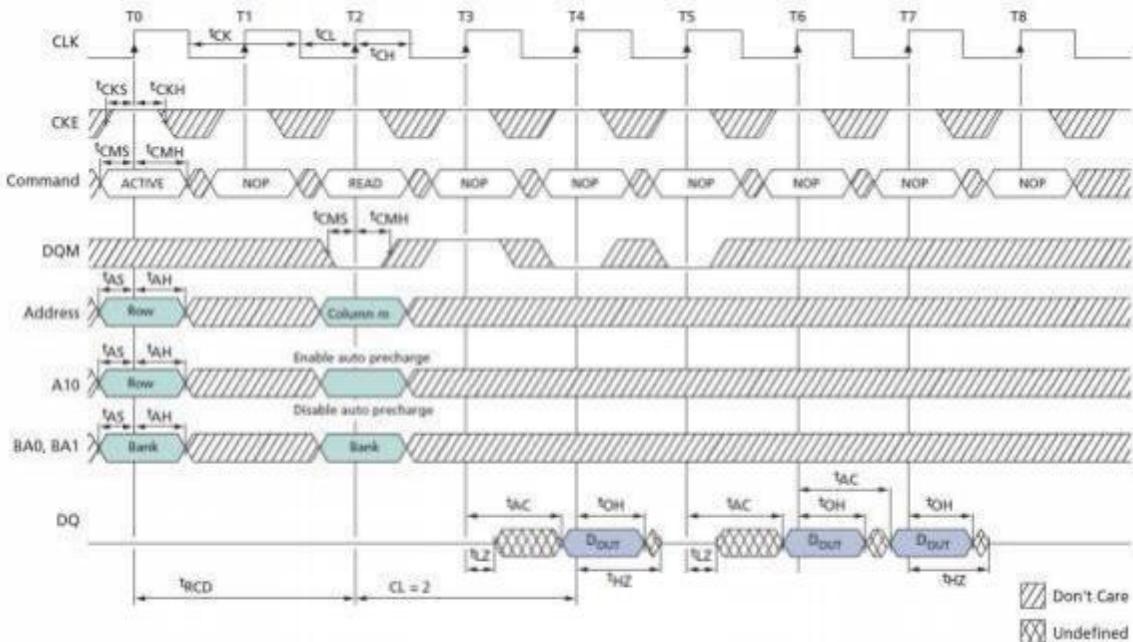

#### 2.2.4. 读取操作

突发读取操作是通过读取命令实现的，如图 2-4 所示。在读取命令中提供开始读取数据的 Column 和 Bank，同时地址线 A10 决定是否使能自动预充电。如果自动预充电使能，则在突发读取操作完成后，自动的对操作的 Row 进行预充电。如果不使能自动预充电，操作的 Row 将保持开启状态。

在突发读取操作中，在读取命令以后，从开始的 Column 地址读取的数据经过 CAS 延迟后，连续的在 CLK 时钟的上升沿出现在数据总线上，当完成突发读取操作后，数据线保持 High-Z。

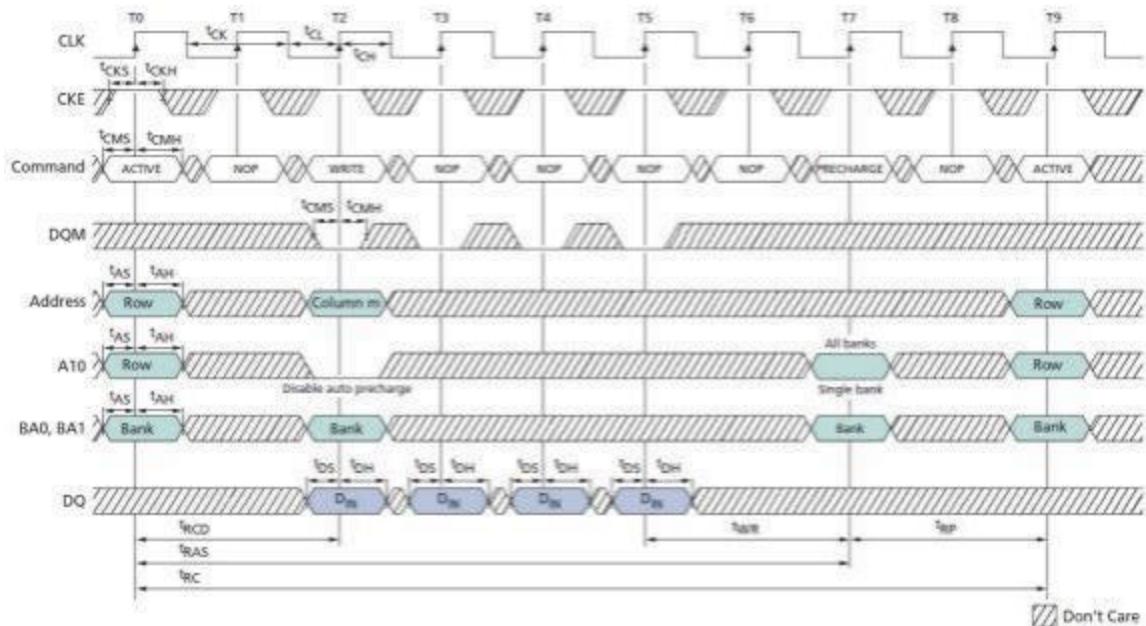

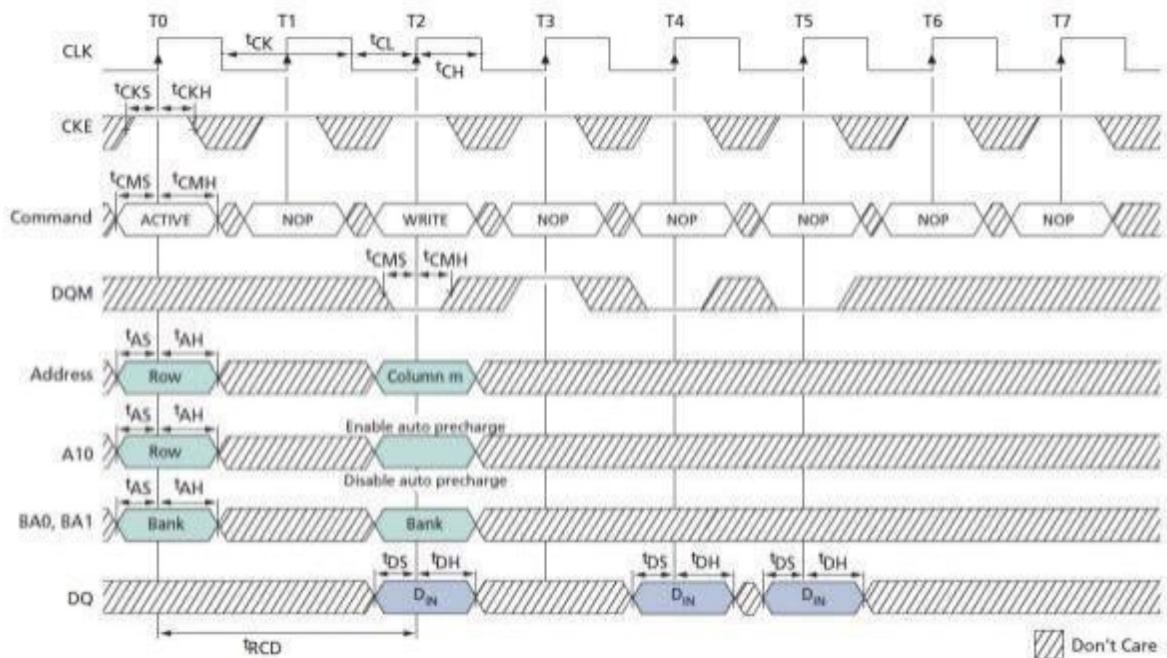

#### 2.2.5. 写入操作

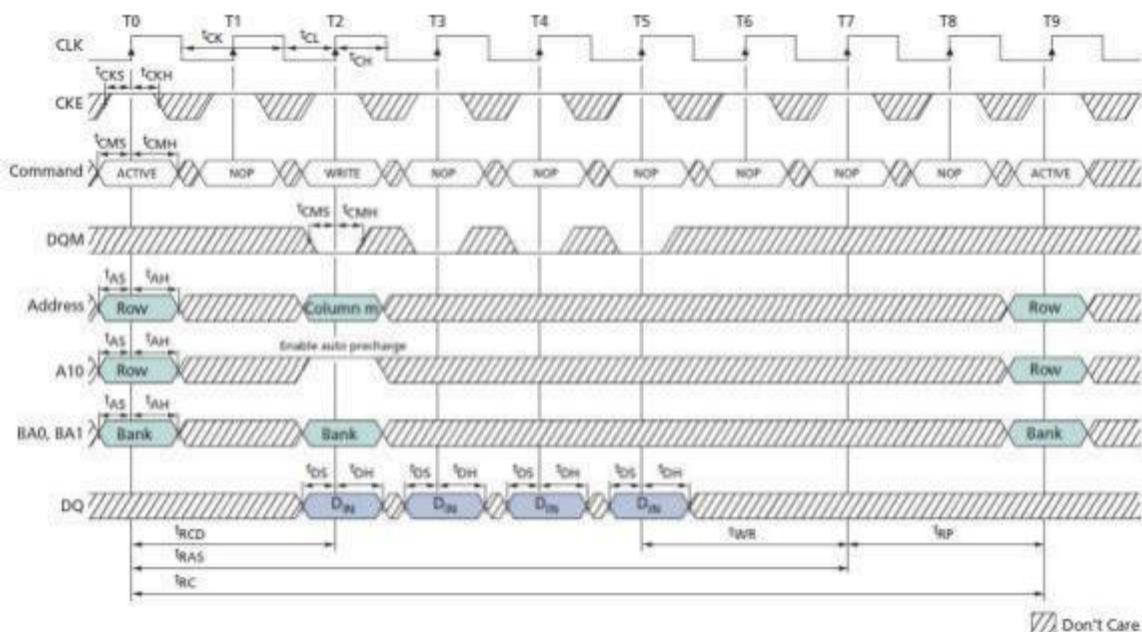

突发写入操作通过写入命令实现，如图 2-5 所示。在写入命令中，提供开始写入的 Column 和 Bank 地址，同时地址线 A10 决定是否使能自动预充电。如果自动预充电使能，则在突发写入操作完成后，自动的对操作的 Row 进行预充电。如果不使能自动预充电，操作的 Row 将保持开启状态。

在突发写入操作中，第一个写入的数据在写入命令的时候被锁存，随后的数据

在每个时钟的上升沿进行锁存。当完成一个固定长度的突发写入后，DQs 会保持高阻，这时后续输入的数据则被忽略。

图 2-5 写入命令时序

图 2-6 预充电命令时序

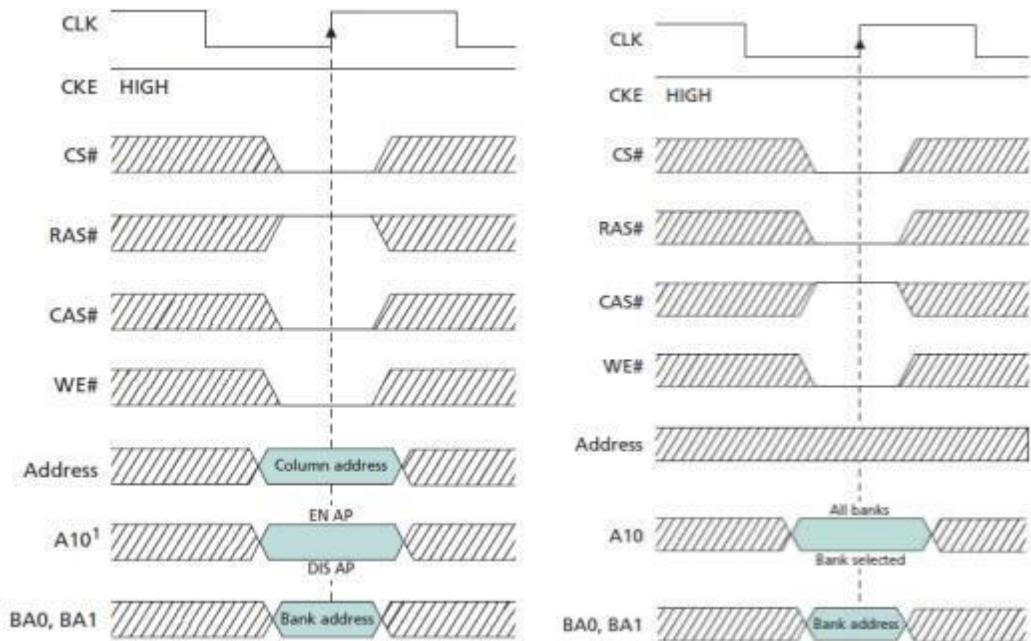

## 2.2.6. 预充电

预充电命令时序图 2-6 所示，其是用来关闭某个 BANK 已经激活的 Row 或者所有 BANK 已经激活的 Row。A10 管脚用来决定是单个 BANK 进行预充电还是所有 BANK 进行预充电。一旦 BANK 被预充电以后，则整个 BANK 处于空闲状态，如果后续需要对此 BANK 进行读写操作，则需要重新激活后才能使用。

## 2.2.7. 自动刷新

由于 DRAM 芯片的存储单元存在漏电现象，为了保持每个存储单元数据的正确性，需要不断的进行刷新操作才能保持芯片数据不丢失。每个存储电容的数据有效保持时间为 64ms，这意味着每一行在 64ms 内都需要被刷新到，对于 256Mb SDRAM 芯片，其总共有 8192 行，所以每隔 7.8us 就需要发送一次自动刷新命令来保证每行都能被及时刷新。

在进行自动刷新操作时，地址由内部刷新计数器自动的依次生成行地址。自动刷新时序图如图 2-7 所示：

图 2-7 自动刷新 (Auto Refresh) 模式时序

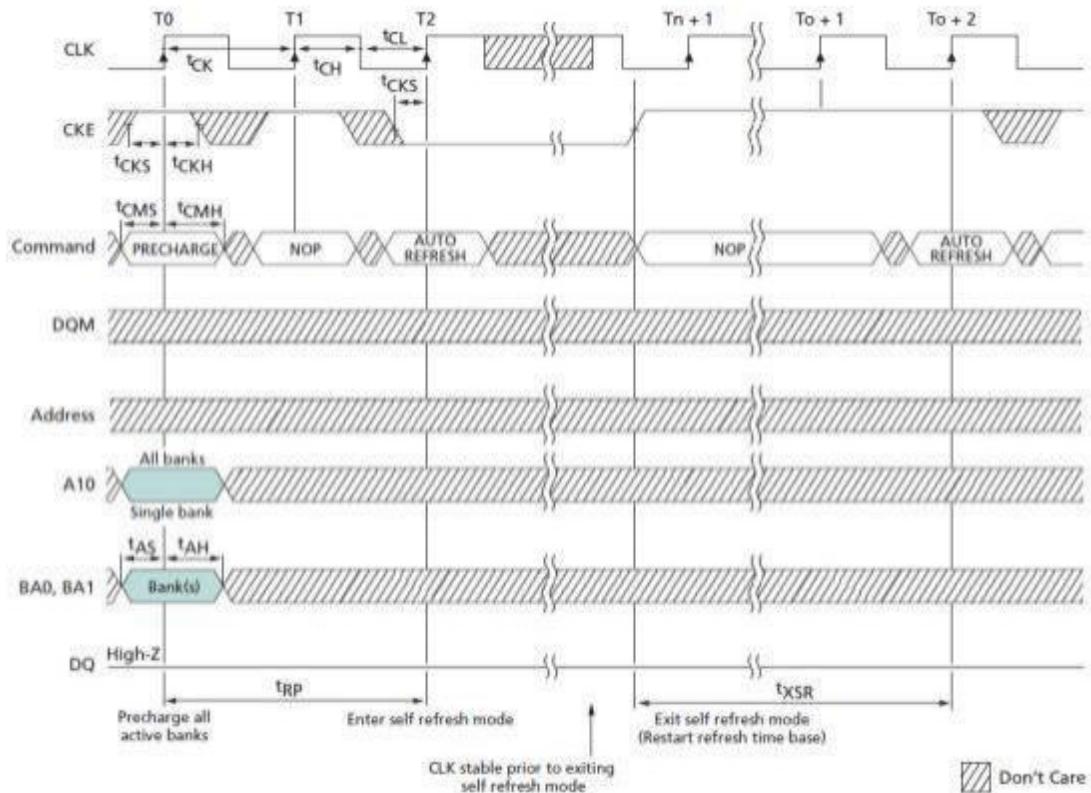

### 2.2.8. 自刷新

自刷新是当系统处于空闲状态或 Power-Down 模式时，用来保持芯片数据不丢失的操作。一旦芯片进入自刷新模式，不需要外部系统提供时钟，而由芯片产生内部时钟，用来执行芯片内部的自动刷新操作。自刷新期间除了 CKE 之外的所有外部信号都是无效的(无需外部提供刷新指令)，只有重新使 CKE 有效才能退出自刷新模式并进入正常操作状态。自刷新的时序图如图 2-8 所示：

图 2-8 自刷新 (Self Refresh) 模式时序

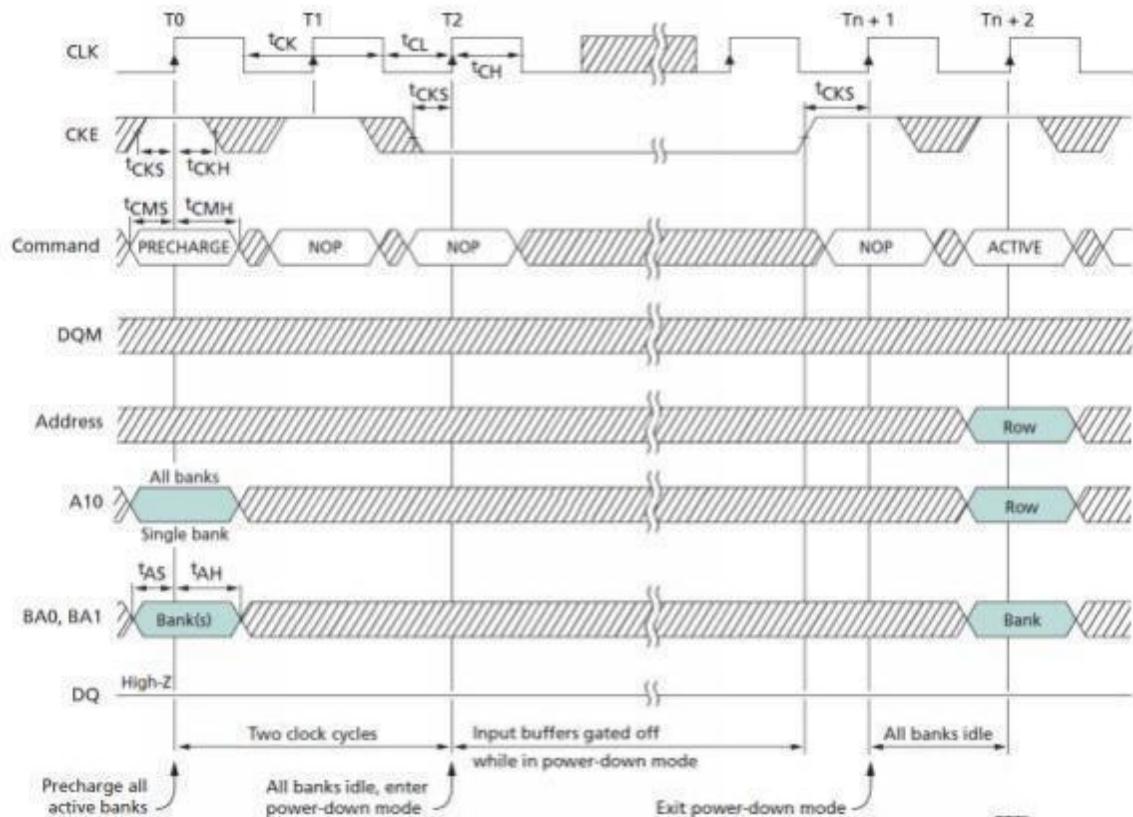

### 2.2.9. Power-Down

当 CKE 保持为低的时候，只有 NOP 指令或没有命令操作时，芯片就进入 Power-Down 模式。当 Power-Down 发生的时候，所有 BANK 处于空闲状态，此时的 Power-Down 称为预充电 Power-Down 模式；当 Power-Down 发生的时候，有 BANK 的 Row 处于激活状态，则称为激活 Power-Down 模式。进入 Power-Down 模式以后，芯片会禁止所有的输入输出，降低功耗，处于待机状态，但时间不能超过刷新周期，防止芯片数据丢失。当 CKE 置高后，经过 tCKS 的延时，就可以退出 Power-Down 模式，如图 2-9 所示。

图 2-9 Power-Down 模式时序

### 2.2.10. 时序图

图 2-10 时钟挂起模式时序

图 2-11 读取操作-不带自动预充电时序

图 2-12 读取操作-带自动预充电时序

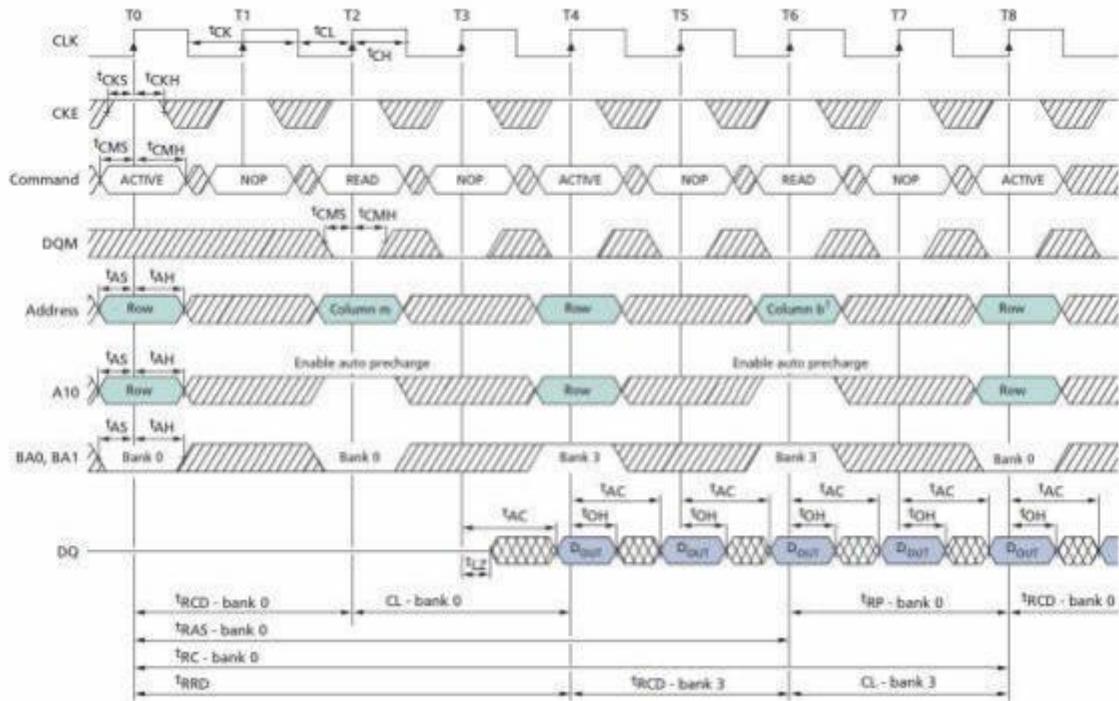

图 2-13 交替 BANK 读取操作时序

图 2-14 DQM 控制的读取操作时序

图 2-15 写入操作-不带自动预充电时序

图 2-16 写入操作-带自动预充电时序

图 2-17 交替 BANK 写入操作时序

图 2-18 DQM 控制的写入操作时序

### 3 电特性

#### 3.1 绝对最大额定值

绝对最大额定值如下：

|                                  |       |                |

|----------------------------------|-------|----------------|

| 电源 电压( $V_{DD}$ 、 $V_{DDQ}$ )    | ..... | 1.0 V ~ +4.6V  |

| 输入/输出 电压( $V_{IN}$ 、 $V_{OUT}$ ) | ..... | 1.0 V ~ +4.6V  |

| 贮存 温度 范围 ( $T_{stg}$ )           | ..... | -65°C ~ +150°C |

| 结温( $T_j$ )                      | ..... | 150°C          |

#### 3.2 推荐工作条件

推荐工作条件如下：

|                               |       |                |

|-------------------------------|-------|----------------|

| 电源 电压( $V_{DD}$ 、 $V_{DDQ}$ ) | ..... | 3.3V±0.3V      |

| 工作 温度 范围 ( $T_A$ )            | ..... | -55°C ~ +125°C |

| 工作 频 率( $f$ )                 | ..... | 133 MHz        |

### 3.3 直流 (DC) 特性表

表 3-1 直流(DC)电特性

| 特性                     | 符号        | 测试条件<br>除另有规定外, $V_{SS} = V_{SSQ} = 0V$ ,<br>$V_{DD} = V_{DDQ} = 3.3V \pm 0.3V$<br>$-55^{\circ}C \leq T_A \leq 125^{\circ}C$ | 最小值 | 最大值 | 单位            |

|------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------|

| 输入高电平                  | $V_{IH}$  | --                                                                                                                           | 2.0 | --  | V             |

| 输入低电平                  | $V_{IL}$  | --                                                                                                                           | --  | 0.8 | V             |

| 输出高电平                  | $V_{OH}$  | $I_{OH} = -2.0\text{ mA}$                                                                                                    | 2.4 | --  | V             |

| 输出低电平                  | $V_{OL}$  | $I_{OL} = 2.0\text{ mA}$                                                                                                     | --  | 0.4 | V             |

| 输入漏电流                  | $I_{IL}$  | $0V \leq V_N \leq V_{DD}$                                                                                                    | -10 | +10 | $\mu\text{A}$ |

| 输出漏电流                  | $I_{OL}$  | $0V \leq V_{OUT} \leq V_{DDQ}$                                                                                               | -10 | +10 | $\mu\text{A}$ |

| 工作电流: 激活模式             | $I_{DD1}$ | Burst=1, 读取或者写入操作, 最小tRC                                                                                                     | --  | 65  | mA            |

| 待机电流:<br>Power-Down 模式 | $I_{DD2}$ | $CKE = 0$ , 所有BANK 未激活                                                                                                       | --  | 10  | mA            |

| 待机电流: 激活模式             | $I_{DD3}$ | $CS\# = 1$ , $CKE = 1$ , tRCD 有效后, 激活所有BANK 并保持该状态                                                                           | --  | 30  | mA            |

| 工作电流: 突发模式             | $I_{DD4}$ | 连续突发, 读取或者写入模式, 所有BANK 激活, $t_{CK} = t_{CK}(\text{min})$                                                                     | --  | 65  | mA            |

| Auto refresh 电流        | $I_{DD5}$ | Auto refresh 模式, $t_{RC} \geq t_{RC}(\text{min})$                                                                            | --  | 85  | mA            |

| Selfrefresh 电流         | $I_{DD6}$ | Selfrefresh 模式, $CKE = 0$                                                                                                    | --  | 10  | mA            |

### 3.4 交流 (AC) 特性表

表 3-2 交流(AC)电特性

| 参数                 | 符号        | 测试条件<br>除另有规定外, $V_{SS} = V_{SSQ} = 0V$ ,<br>$V_{DD} = V_{DDQ} = 3.3V \pm 0.3V$<br>$-55^{\circ}C \leq T_A \leq 125^{\circ}C$ | 最小  | 最大  | 单位 |

|--------------------|-----------|------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|

| 时钟周期 (CL=3)        | $t_{CK}$  | 见图 2-11、图 2-12、图 2-15、图 2-16                                                                                                 | 7   | --  | ns |

| 数据输出延时             | $t_{AC}$  | 见图 2-11、图 2-12                                                                                                               | --  | 5.4 | ns |

| 地址保持时间             | $t_{AH}$  | 见图 2-11、图 2-12、图 2-15、图 2-16                                                                                                 | 0.8 | --  | ns |

| 地址建立时间             | $t_{AS}$  | 见图 2-11、图 2-12、图 2-15、图 2-16                                                                                                 | 1.5 | --  | ns |

| CLK 高电平宽度          | $t_{CH}$  | 见图 2-11、图 2-12、图 2-15、图 2-16                                                                                                 | 2.5 | --  | ns |

| CLK 低电平宽度          | $t_{CL}$  | 见图 2-11、图 2-12、图 2-15、图 2-16                                                                                                 | 2.5 | --  | ns |

| CKE 保持时间           | $t_{CKH}$ | 见图 2-11、图 2-12、图 2-15、图 2-16                                                                                                 | 0.8 | --  | ns |

| CKE 建立时间           | $t_{CKS}$ | 见图 2-11、图 2-12、图 2-15、图 2-16                                                                                                 | 1.5 | --  | ns |

| CS#、RAS#、CAS#、WE#、 | $t_{CMH}$ | 见图 2-11、图 2-12、图 2-15、图                                                                                                      | 0.8 | --  | ns |

| 参数                                        | 符号                | 测试条件<br>除另有规定外, $V_{SS}=V_{SSQ}=0V$ ,<br>$V_{DD}=V_{DDQ}=3.3V\pm0.3V$<br>$-55^{\circ}C \leq T_A \leq 125^{\circ}C$ | 最小   | 最大   | 单位 |

|-------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------|------|------|----|

| DQM 保持时间                                  |                   | 2-16                                                                                                               |      |      |    |

| CS#、RAS#、CAS#、WE#、<br>DQM 建立时间            | t <sub>CMS</sub>  | 见图 2-11、图 2-12、图 2-15、<br>图 2-16                                                                                   | 1.5  | --   | ns |

| 数据输入保持时间                                  | t <sub>DH</sub>   | 见图 2-15、图 2-16                                                                                                     | 0.8  | --   | ns |

| 数据输入建立时间                                  | t <sub>DS</sub>   | 见图 2-15、图 2-16                                                                                                     | 1.5  | --   | ns |

| 输出高阻延时                                    | t <sub>HZ</sub>   | 见图 2-11、图 2-12                                                                                                     | --   | 5.4  | ns |

| 输出低阻延时                                    | t <sub>LZ</sub>   | 见图 2-11、图 2-12                                                                                                     | 0    | --   | ns |

| 数据输出保持时间                                  | t <sub>OH</sub>   | 见图 2-11、图 2-12                                                                                                     | 2.5  | --   | ns |

| ACTIVE 到预充电指令延<br>时                       | t <sub>TRAS</sub> | 见图 2-11、图 2-12、图 2-15、<br>图 2-16                                                                                   | 42   | 100K | ns |

| ACTIVE 到 ACTIVE 指<br>令延<br>时              | t <sub>TRC</sub>  | 见图 2-11、图 2-12                                                                                                     | 63   | --   | ns |

| ACTIVE 到读或写延时                             | t <sub>TRCD</sub> | 见图 2-11、图 2-12、图 2-15、<br>图 2-16                                                                                   | 21   | --   | ns |

| 刷新周期<br>(-55°C ~ 105°C)                   | t <sub>REF</sub>  | --                                                                                                                 | --   | 64   | ms |

| 刷新周期<br>(105°C ~ 125°C)                   | t <sub>REF</sub>  | --                                                                                                                 | --   | 32   | ms |

| 自动刷新指令周期                                  | t <sub>TRFC</sub> | 见图 2-2、图 2-7                                                                                                       | 63   | --   | ns |

| 预充电指令周期                                   | t <sub>TRP</sub>  | 见图 2-2、图 2-7、图 2-8                                                                                                 | 21   | --   | ns |

| ACTIVE Bank A 到<br>ACTIVE Bank B 指令间<br>隔 | t <sub>TRRD</sub> | 见图 2-13、图 2-17                                                                                                     | 14   | --   | ns |

| 写恢复时间                                     | t <sub>TWR</sub>  | 见图 2-15、图 2-16                                                                                                     | 14   | --   | ns |

| 自刷新退出到ACTIVE<br>指<br>令时间                  | t <sub>TXSR</sub> | 见图 2-8                                                                                                             | 64.5 | --   | ns |

| a 该参数不要求测试。                               |                   |                                                                                                                    |      |      |    |

## 4 说明事项

### 4.1 运输与储存

芯片在适宜环境下储运。

使用指定的防静电包装盒进行产品的包装和运输。在运输过程中，确保芯片不要与外物发生碰撞。

### 4.2 开箱与检查

开箱使用芯片时，请注意观察产品标识。确定产品标识清晰，无污迹，无擦痕。同时，注意检查无损坏，无伤痕，管脚整齐，无缺失，无变形。

### 4.3 使用操作规程及注意事项

器件必须采取防静电措施进行操作。取用芯片时应佩戴防静电手套，防止人体电荷对芯片的静电冲击，损坏芯片。将芯片插入电路板上的底座时以及将芯片从电路板上的底座取出时，应注意施力方向以确保芯片管脚均匀受力。不要因为用力过猛，损坏芯片管脚，导致无法使用。

推荐下列操作措施：

- a) 器件应在防静电的工作台上操作，或带指套操作；

- b) 试验设备和器具应接地；

- c) 不能触摸器件引线；

- d) 器件应存放在导电材料制成的容器中（如：集成电路专用盒）；

- e) 生产、测试、使用以及转运过程中应避免使用引起静电的塑料、橡胶或丝织物；

- f) 相对湿度尽可能保持在 50%±30%。

### 4.4 质量保证

公司质量管理体系根据国军标 GJB9001 要求制定了完善的质量管理工作流程，对产品的设计、生产和销售进行日常质量管理。产品制定依据 GJB7400《合格制造厂认证用半导体集成电路通用规范》裁剪后的标准进行设计和生产，并 GJB548《微电子器件试验方法和程序》的要求进行试验和检验。产品兼容性好、可靠性高。

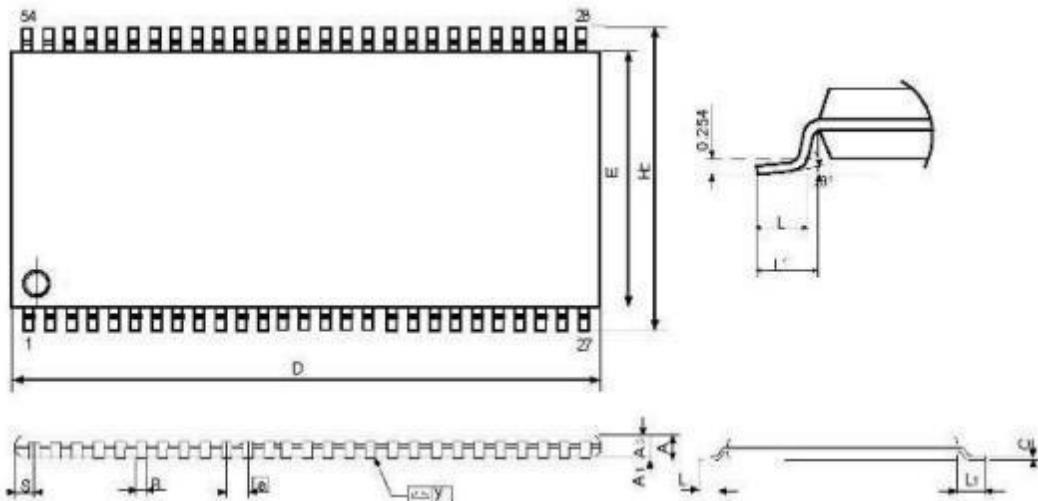

## 5 封装尺寸

### 5.1 TSOP54 外形尺寸图

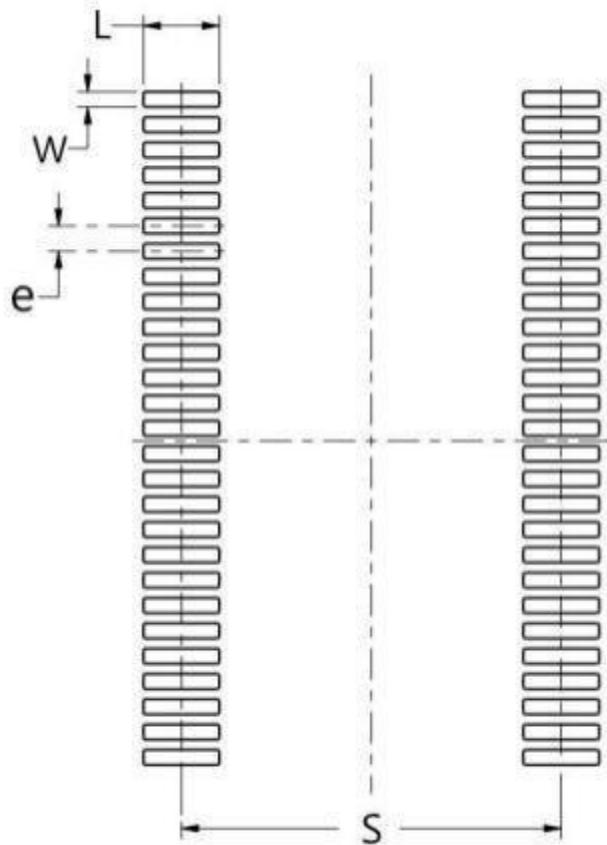

采用 TSOP54 封装，具体封装尺寸如图 5-1。

| 尺寸符号 | 数值 (单位: mm) |       |       |

|------|-------------|-------|-------|

|      | 最小值         | 公称值   | 最大值   |

| A    | --          | --    | 1.2   |

| A1   | 0.05        | --    | 0.2   |

| A2   | 0.9         | 1.0   | 1.1   |

| B    | 0.25        | 0.35  | 0.45  |

| C    | 0.12        | 0.165 | 0.21  |

| D    | 22.09       | 22.22 | 22.35 |

| E    | 10.03       | 10.16 | 10.29 |

| e    | 0.8         |       |       |

| HE   | 11.56       | 11.76 | 11.96 |

| L    | 0.4         | 0.5   | 0.6   |

| L1   | --          | 0.84  | --    |

| S    | --          | 0.71  | --    |

| y    | --          | --    | 0.1   |

| Θ    | 0 °         | --    | 8 °   |

图 5-1 TSOP54 封装外形尺寸图

## 5.2 器件重量

TLX48LCM1616 的重量约为0.573g。

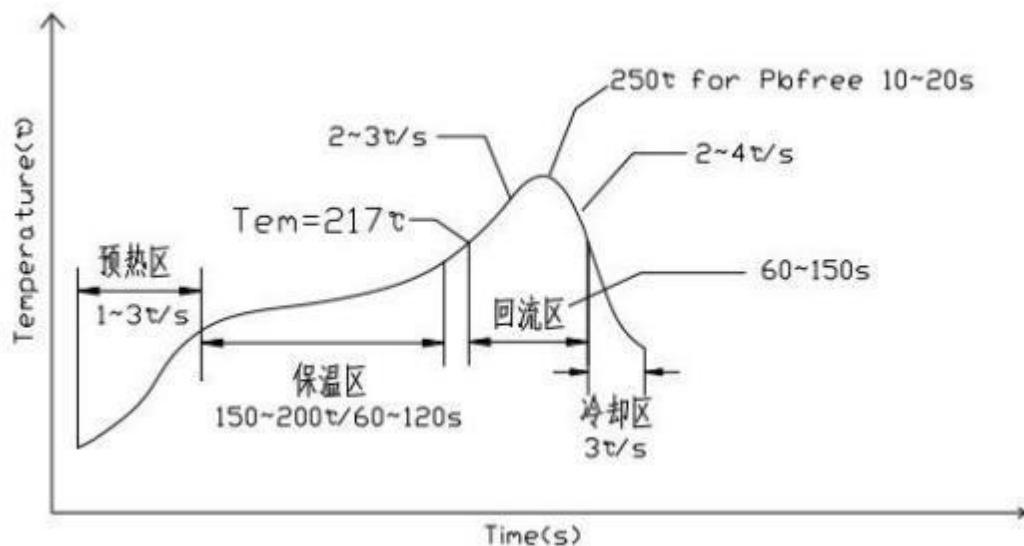

## 5.3 推荐焊装工艺

TLX48LCM1616 采用无铅回流焊温度，如图 5-2 所示。

图 5-2 无铅回流焊曲线图

该器件采用塑封工艺，属于非气密性封装，具有水密性，芯片引线材料为铜，引脚涂覆 为锡。

## 5.4 推荐焊盘尺寸

产品推荐的焊盘如下图：

单位：mm

| 器件型号         | 封装形式   | e   | S  | L   | W   |

|--------------|--------|-----|----|-----|-----|

| TLX48LCM1616 | TSOP54 | 0.8 | 11 | 1.7 | 0.5 |

## 6 订货信息

### 6.1 选型列表

表 6-1 选型列表

| 订购型号           | 温度等级            | 封装类型 | 器件标识          | MSL    | 质量等级   |

|----------------|-----------------|------|---------------|--------|--------|

| JTLX48LCM1616  | -55 °C ~+125 °C | TSOP | TLX48LCM1616  | MSL1/3 | N1/军温级 |

| JTLX48LCM1616Q | -55 °C ~+125 °C | TSOP | TLX48LCM1616Q | MSL1/3 | N1/军温级 |

| JTLX48LCM1616J | -55 °C ~+125 °C | TSOP | TLX48LCM1616J | MSL1/3 | N1/军温级 |

| TLX48LCM1616   | -40 °C ~+125 °C | TSOP | TLX48LCM1616  | MSL1/3 | 工业级    |

| TLX48LCM1616Q  | -40 °C ~+125 °C | TSOP | TLX48LCM1616Q | MSL1/3 | 工业级    |

| TLX48LCM1616J  | -40 °C ~+125 °C | TSOP | TLX48LCM1616J | MSL1/3 | 工业级    |