无锡泰连芯科技有限公司

**TLX925** 型

SSC 低功耗 LVC MOS 时钟产生器

2024 年 06 月

# 支持 SSC 低功耗 LVC MOS 时钟产生器

## 1 主要性能

- 2 个独立 PLL，5 路通道输出

- 支持 EEPROM 烧写和 I2C 读写

- 灵活的时钟输入

片外晶振：8MHz~32MHz

- 片内 VCXO 模式

- 单端 LVC MOS 输入

- 独立的通道输出时钟，最高支持 230MHz

- 独立通道供电电压，支持 1.8V~3.3V

- 灵活的时钟驱动

3 个自定义的片外引脚控制（S2、S1，S0），支持 SSC 选择，频率切换，输出状态控制等。

可编程的 SSC 深度选择；

- 1.8V 供电

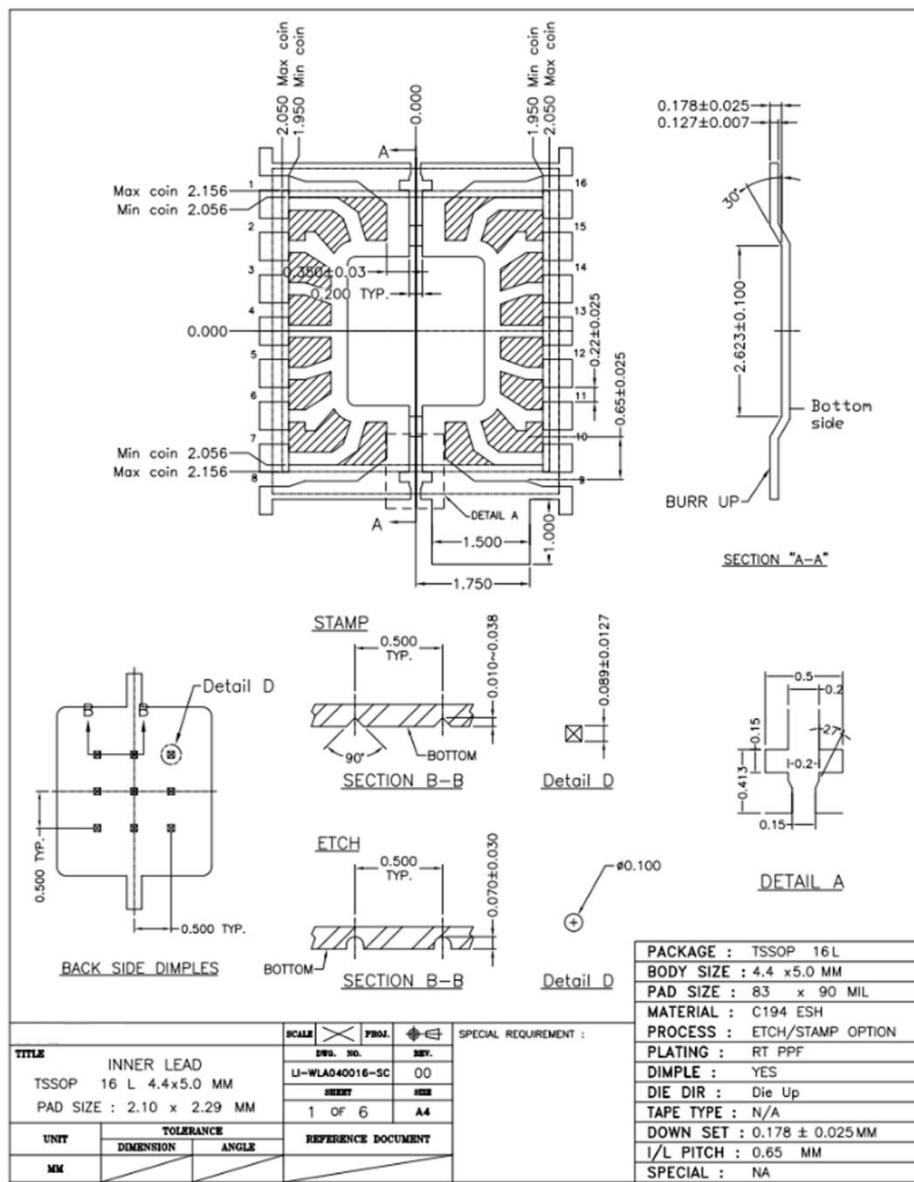

- TSSOP 引脚封装

- 工业级工作温度范围：-55°C~125°C

## 3 产品特点

- 低功耗，可编程时钟产生器

- 支持 5 路通道独立输出频率，最高可达 230MHz

- 通道供电电压支持 1.8V~3.3V

- 支持时钟扩频，降低 EMI 影响

- 支持晶振输入，片内 VCXO，LVC MOS 输入。晶振输入时，可支持负载电容调节，最大可达 20pF

- 质量等级：军温级&N1 级

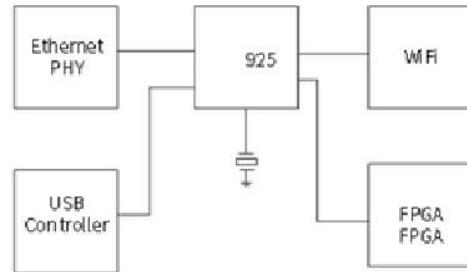

图 1 TLX925 典型应用场合

## 2 应用场合

- 打印机，DVD 记录器，DVD 播放器

D-TV, STBs, IP-STBs

**Table of Contents**

|                      |    |

|----------------------|----|

| 1 主要性能 .....         | 2  |

| 2 应用场合 .....         | 2  |

| 3 产品特点 .....         | 2  |

| 4 版本信息 .....         | 4  |

| 5 概述 .....           | 5  |

| 6 ESD 保护 .....       | 6  |

| 7 引脚配置与功能描述 .....    | 7  |

| 8 技术规格 .....         | 8  |

| 8.1 电气特性 .....       | 8  |

| 8.2 EEPROM .....     | 10 |

| 8.3 功耗 .....         | 10 |

| 8.4 功能模块 .....       | 11 |

| 8.5 I2C .....        | 13 |

| 8.6 寄存器 .....        | 15 |

| 9 应用细节 .....         | 19 |

| 9.1 通道输出频率设置 .....   | 19 |

| 9.2 时钟扩频 (SSC) ..... | 20 |

| 10 外形尺寸 .....        | 23 |

## 4 版本信息

| 版本号 | 日期         | 注释   |

|-----|------------|------|

| A.0 | 2023/08/25 | 初始版本 |

## 5 概述

一款低功耗五路 LVC MOS 时钟输出，具有 SSC 功能（包括中心扩频和下扩频），芯片封装采用 TSSOP 16Pin。三路输出时钟频率是可调的，输出范围最大可达 230M。输入参考时钟采用具有 VCXO 型的晶振，频率输入范围可达 8M~32M。内部包含 I2C 数据传输和掉电不丢失的 EEPROM 寄存器

## 6 ESD 保护

带电器件和电路板可能会在没有察觉的情况下放电。尽管本产品具有专利或专有保护电路，但在遇到高能量 ESD 时，器件可能会损坏。因此，应当采取适当的 ESD 防范措施，以避免器件性能下降或功能丧失。

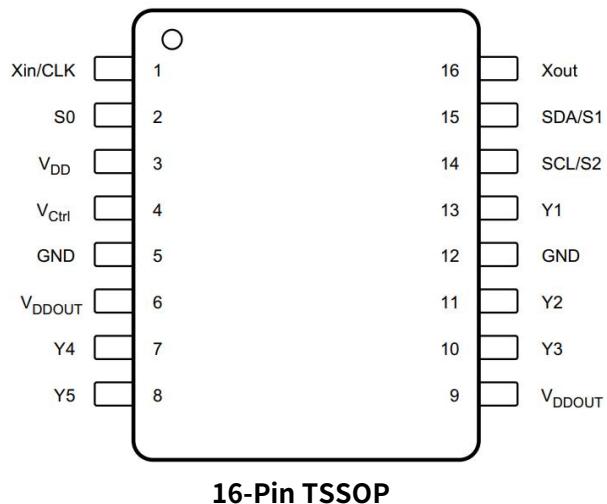

## 7 引脚配置与功能描述

俯视图

### 管脚定义

| 管脚号   | 名称      | IO 类型 | 功能描述                                                                                                                                    |

|-------|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 5, 12 | GND     |       | 地                                                                                                                                       |

| 14    | SCL/S2  | I     | 复用引脚, 当作为 SCL 功能时, 作为数据通信功能, 且内部有上拉的 500K 电阻, 该 IO 是 LVCMOS 接口。当作为 S2 功能时, 可通过同时配置 S0, S1, 控制三路输出的状态, 为 0, 三态, pd, 或者 bypass。默认是 SCL 功能 |

| 15    | SDA/S1  | I/O   | 复用引脚, 当作为 SDA 功能时, 作为数据通信功能, 且内部有上拉的 500K 电阻, 该 IO 是 LVCMOS 接口。当作为 S1 功能时, 可通过同时配置 S0, S2, 控制三路输出的状态, 为 0, 三态, pd, 或者 bypass。默认是 SDA 功能 |

| 2     | S0      | I     | LVCMOS 输入形式, 内部也有 500K 电阻的上拉                                                                                                            |

| 4     | VCtrl   | I     | 通过外部输入电压调节晶振的输出频率, 频率输出范围是+-150ppm, 当不使用该功能时, 上拉或者悬空                                                                                    |

| 3     | VDD     | P     | 1.8V 电源, 给 core 供电                                                                                                                      |

| 6,9   | VDDOUT  | P     | 给 LVCMOS 接口提供电源 1.8V                                                                                                                    |

| 1     | Xin/CLK | I     | 晶振输入信号或者可以直接灌入一个 LVCMOS 输入时钟, 该配置可通过 SCL/SDA 控制                                                                                         |

| 16    | Xout    | O     | 晶振输出信号, 当不使用时, 悬空或者上拉                                                                                                                   |

| 13    | Y1      | O     | LVCMOS 输出, 可独自输出频率, 最高频率可达 230M,                                                                                                        |

| 11    | Y2      | O     | LVCMOS 输出, 可独自输出频率, 最高频率可达 230M                                                                                                         |

| 10    | Y3      | O     | LVCMOS 输出, 可独自输出频率, 最高频率可达 230M                                                                                                         |

| 7     | Y4      | O     | LVCMOS 输出, 可独自输出频率, 最高频率可达 230M                                                                                                         |

| 8     | Y5      | O     | LVCMOS 输出, 可独自输出频率, 最高频率可达 230M                                                                                                         |

## 8 技术规格

### 8.1 电气特性

表 1 工作条件

|            |                    | 最小 | 典型      | 最大 | 单位  |

|------------|--------------------|----|---------|----|-----|

| VDD        | 芯片供电电压             |    | 1.8     |    | V   |

| VDDOUT     | 输出 Yx 的供电电压        |    | 1.8/3.3 |    | V   |

| VI(thresh) | LVC MOS 输入阈值       |    | 0.8     |    | V   |

| TA         | 环境温度               |    | 27      |    | °C  |

| 晶振         |                    |    |         |    |     |

| fxtal      | 晶振频率               |    | 25      |    | MHz |

| CL         | XIN 和 Xout 端芯片集成负载 | 0  | 10      | 20 | pF  |

除另有说明, 以下测试电源电压和温度均在典型工作条件。

表 2 电气特性指标

| 参数                       | 测试条件                                               | 最小         | 典型    | 最大     | 单位  |

|--------------------------|----------------------------------------------------|------------|-------|--------|-----|

| IDD VDD 端供电电流            | 输出关断,<br>fclk=27MHz,<br>fvco=135MHz,<br>fout=27MHz | 8.56       | 5.9   | 7.6    | mA  |

|                          | 2 个 PLL 工作                                         |            |       |        |     |

| IDDOUT VDDOUT 端供电电流      | 空载, 所有输出导通, fout=27MHz                             |            |       | 3.7    | mA  |

| fvco PLL 中的 VCO 输出频率     |                                                    | 80         | 230   |        | MHz |

| LVC MOS 输出特性 VDDOUT=3.3V |                                                    |            |       |        |     |

| VOH LVC MOS 高阈值输出电压      | VDDOUT=3V, IOH=-0.1mA                              | 2.975      | 2.77  | 0.0060 | V   |

|                          | VDDOUT=3V, IOH=-8mA                                |            |       |        |     |

|                          | VDDOUT=3V, IOH=-12mA                               | 2.66       |       |        |     |

| VOL LVC MOS 低阈值输出电压      | VDDOUT=3V, IOL=0.1mA                               | 0.139      | 0.139 | 0.206  | V   |

|                          | VDDOUT=3V, IOL=8mA                                 |            |       |        |     |

|                          | VDDOUT=3V, IOL=12mA                                | 0.206      |       |        |     |

| tPLH, tPHL 输入输出延时        | PLL 旁路                                             | 4.8/4.9    |       |        | nS  |

| tr/tf 上升沿和下降沿时间          | VDDOUT=3.3V (20%-80%)                              | 0.322/0.28 |       |        | nS  |

| tjit (Tie) 绝对抖动          | 1 个 PLL 开通, Y2-Y3 <sup>(1)</sup>                   | 120        | 135   | 30     | pS  |

|                          | 2 个 PLL 开通, Y2-Y5 <sup>(1)</sup>                   |            |       |        |     |

| tjit (cc) 周期差抖动          | 1 个 PLL 开通, Y2-Y3 <sup>(1)</sup>                   | 30         | 30    | 110    | pS  |

|                          | 2 个 PLL 开通, Y2-Y5 <sup>(1)</sup>                   |            |       |        |     |

| tjit (per) 周期抖动峰峰值       | 1 个 PLL 开通, Y2-Y3 <sup>(1)</sup>                   | 110        | 115   | 115    | pS  |

|                          | 2 个 PLL 开通, Y2-Y5 <sup>(1)</sup>                   |            |       |        |     |

|                          |                                  |            |    |

|--------------------------|----------------------------------|------------|----|

| tsk(o) 输出偏斜              | Fout=50MHz, Y1-Y3                | 55         | pS |

|                          | Fout=50MHz, Y2-Y5                | 80         |    |

| Odc 输出占空比                | Fvco=100MHz, Pdiv=1              | 46.2%      |    |

| LVC MOS 输出特性 VDDOUT=2.5V |                                  |            |    |

| VOH LVC MOS 高阈值输出电压      | VDDOUT=2.3V, IOH=-0.1mA          | 2.275      | V  |

|                          | VDDOUT=2.3V, IOH=-6mA            | 2.098      |    |

|                          | VDDOUT=2.3V, IOH=-10mA           | 1.96       |    |

| VOL LVC MOS 低阈值输出电压      | VDDOUT=2.3V, IOH=0.1mA           | 0.0062     | V  |

|                          | VDDOUT=2.3V, IOH=6mA             | 0.115      |    |

|                          | VDDOUT=2.3V, IOH=10mA            | 0.192      |    |

| tPLH, tPHL 输入输出延时        | PLL 旁路                           | 5.2/7.2    | nS |

| tr/tf 上升沿和下降沿时间          | VDDOUT=2.5V (20%-80%)            | 0.41/0.32  | nS |

| tjit (Tie) 绝对抖动          | 1 个 PLL 开通, Y2-Y3 <sup>(1)</sup> | 160        | pS |

|                          | 2 个 PLL 开通, Y2-Y5 <sup>(1)</sup> | 230        |    |

| tjit (cc) 周期差抖动          | 1 个 PLL 开通, Y2-Y3 <sup>(1)</sup> | 30         | pS |

|                          | 2 个 PLL 开通, Y2-Y5 <sup>(1)</sup> | 42         |    |

| tjit (per) 周期抖动峰峰值       | 1 个 PLL 开通, Y2-Y3 <sup>(1)</sup> | 125        | pS |

|                          | 2 个 PLL 开通, Y2-Y5 <sup>(1)</sup> | 130        |    |

| tsk(o) 输出偏斜              | Fout=50MHz, Y1-Y3                | 40         | pS |

|                          | Fout=50MHz, Y2-Y5                | 80         |    |

| Odc 输出占空比                | Fvco=100MHz, Pdiv=1              | 45.7%      |    |

| LVC MOS 输出特性 VDDOUT=1.8V |                                  |            |    |

| VOH LVC MOS 高阈值输出电压      | VDDOUT=1.7V, IOH=-0.1mA          | 1.674      | V  |

|                          | VDDOUT=1.7V, IOH=-4mA            | 1.516      |    |

|                          | VDDOUT=1.7V, IOH=-8mA            | 1.3        |    |

| VOL LVC MOS 低阈值输出电压      | VDDOUT=1.7V, IOH=0.1mA           | 0.0059     | V  |

|                          | VDDOUT=1.7V, IOH=4mA             | 0.096      |    |

|                          | VDDOUT=1.7V, IOH=8mA             | 0.197      |    |

| tPLH, tPHL 输入输出延时        | PLL 旁路                           | 5.2/7.2    | nS |

| tr/tf 上升沿和下降沿时间          | VDDOUT=1.8V (20%-80%)            | 1.18/0.475 | nS |

| tjit (Tie) 绝对抖动          | 1 个 PLL 开通, Y2-Y3 <sup>(1)</sup> | 112        | pS |

|                          | 2 个 PLL 开通, Y2-Y5 <sup>(1)</sup> | 125        |    |

| tjit (cc) 周期差抖动          | 1 个 PLL 开通, Y2-Y3 <sup>(1)</sup> | 150        | pS |

|                          | 2 个 PLL 开通, Y2-Y5 <sup>(1)</sup> | 40         |    |

| tjit (per) 周期抖动峰峰值       | 1 个 PLL 开通, Y2-Y3 <sup>(1)</sup> | 370        | pS |

|                          | 2 个 PLL 开通, Y2-Y5 <sup>(1)</sup> | 170        |    |

| tsk(o) 输出偏斜              | Fout=50MHz, Y1-Y3                | 92         | pS |

|                          | Fout=50MHz, Y2-Y5                | 111        |    |

|           |                     |       |  |

|-----------|---------------------|-------|--|

| Odc 输出占空比 | Fvco=100MHz, Pdiv=1 | 44.2% |  |

|-----------|---------------------|-------|--|

备注： (1) 晶振频率为 25M, fvco=135M,通道输出频率为 27M

## 8.2 EEPROM

表 3 EEPROM 特性

|            | 最小 | 典型   | 最大 | 单位 |

|------------|----|------|----|----|

| EEcyc 编程周期 |    | 1000 |    | 周期 |

| EEret 数据保留 |    | 10   |    | 年  |

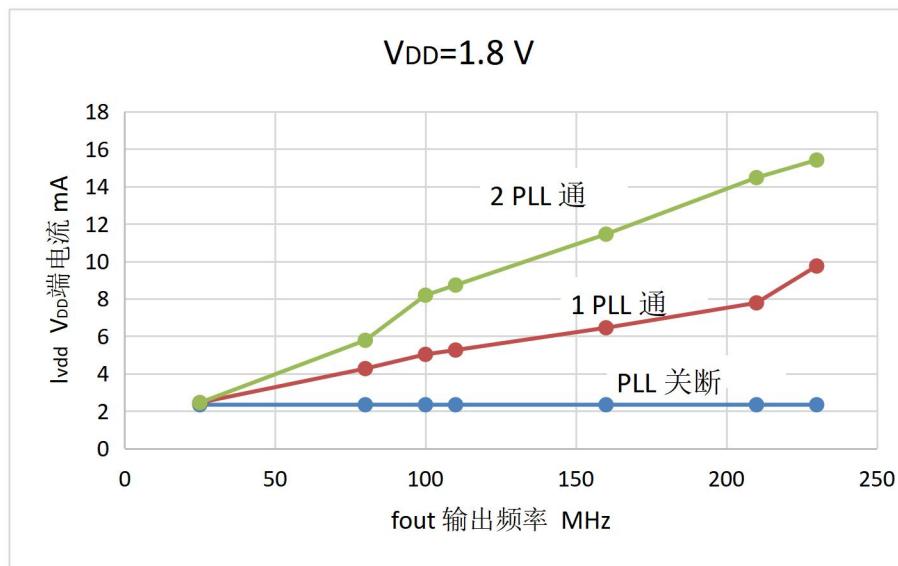

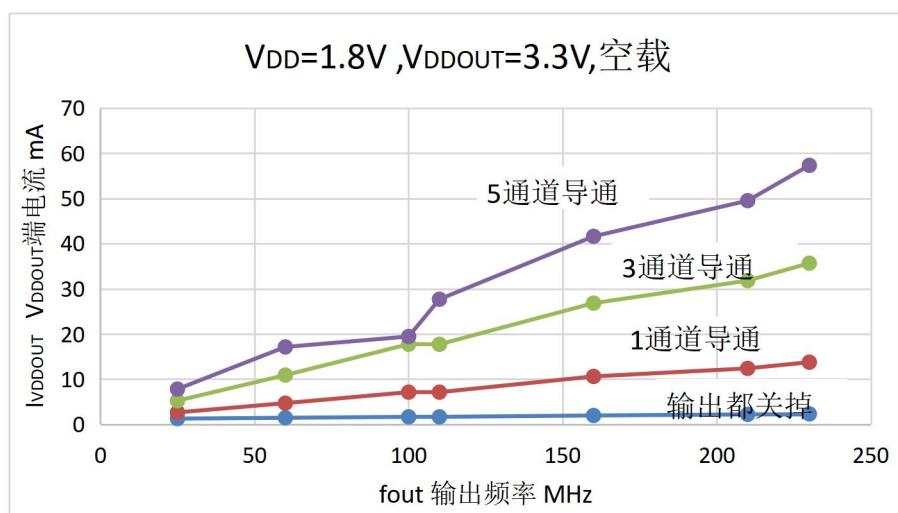

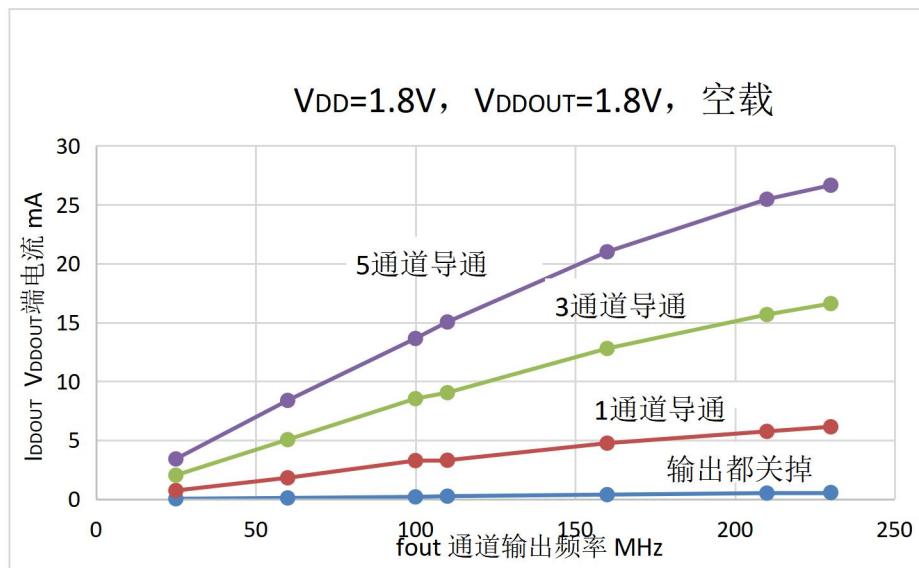

## 8.3 功耗

图 2 VDD 端 1.8V 的功耗与频率关系

图 3 VDDOUT 端 3.3V 的功耗与频率关系

图 4 VDDOUT 端 1.8V 的功耗与频率关系

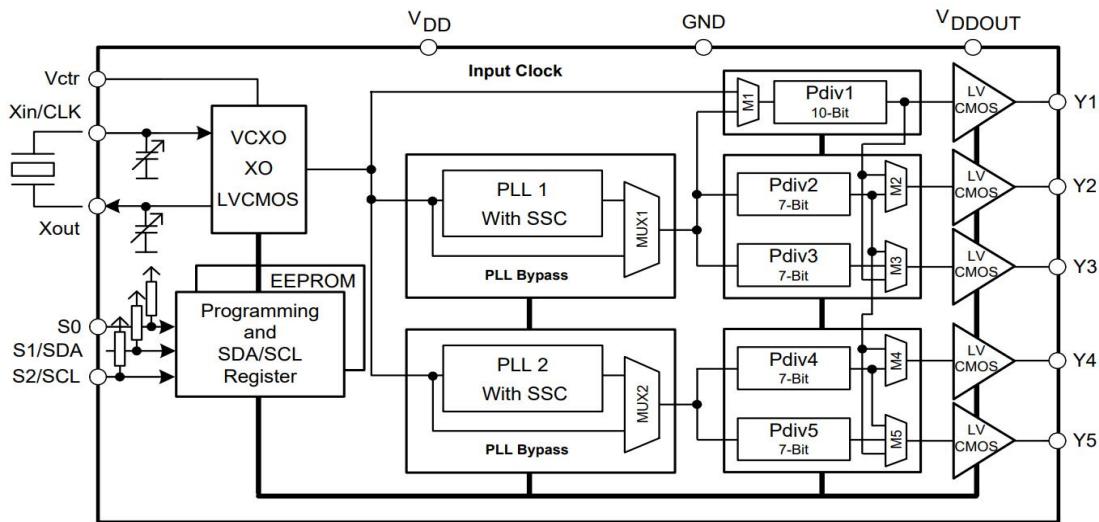

## 8.4 功能模块

图 5 TLX925 模块示意图

TLX925 自带三个片外引脚 S0, S1, S2, 通过这三个引脚可以实现扩频深度 (SSC) 的选择，输出频率范围选择，通道输出状态选择

表 4 SSC 控制表

| SSCx(3bit) |   |   | 中心扩频    | 下扩频     |

|------------|---|---|---------|---------|

| 0          | 0 | 0 | 0% (关断) | 0% (关断) |

| 0          | 0 | 1 | ±0.25%  | -0.25%  |

| 0          | 1 | 0 | ±0.5%   | -0.5%   |

|   |   |   |        |        |

|---|---|---|--------|--------|

| 0 | 1 | 1 | ±0.75% | -0.75% |

| 1 | 0 | 0 | ±1%    | -1%    |

| 1 | 0 | 1 | ±1.25% | -1.25% |

| 1 | 1 | 0 | ±1.5%  | -1.5%  |

| 1 | 1 | 1 | ±2%    | -2%    |

表 5 频率控制表

| 频率选择 |         |

|------|---------|

| FSx  | 功能      |

| 0    | Fvcox_0 |

| 1    | Fvcox_1 |

表 6 YxYx 输出控制表

| 输出状态选择 |          |

|--------|----------|

| YxYx   | 功能       |

| 0      | YxYx_ST0 |

| 1      | YxYx_ST1 |

表 7 Y1 输出控制表

| 输出状态选择 |        |

|--------|--------|

| Y1     | 功能     |

| 0      | Y1_ST0 |

| 1      | Y1_ST1 |

SDA/S1(Pin 15)和 SCL/S2(Pin 14)作为芯片的复用引脚。在默认模式下，这两个 Pin 是作为 SDA/SCL 功能模式，它们可以通过寄存器 02h 的 Bit6 的电平为高，来达到模式的更换。该 bit 不能烧写到 EEPROM。

表 8 出厂后寄存器默认设置 (2)

| 控制 Pin    | Y1        | PLL1 设置 |        |         | PLL2 设置 |        |         |

|-----------|-----------|---------|--------|---------|---------|--------|---------|

|           |           | 频率选择    | SSC 选择 | 输出状态选择  | 频率选择    | SSC 选择 | 输出状态选择  |

| S2        | S1        | S0      | Y1     | FS1     | SSC1    | Y2Y3   | FS2     |

| SCL (I2C) | SDA (I2C) | 0       | 高阻     | Fvc01_0 | off     | 高阻     | Fvc02_0 |

| SCL (I2C) | SDA (I2C) | 1       | 使能     | Fvc01_0 | off     | 使能     | Fvc02_0 |

备注：(1) S1 默认为 SDA, S2 默认为 SCL 功能（或者通过寄存器 02h 的 bit6 设置为 0）。这两个 Pin 没有任何的电平控制功能，但是它们作为 I2C 功能时，可以认为 S2=0, S1=0。S0 一直可以作为电平控制功能。

表 9 S2, S1, S0 配置

|  | Y1 | PLL1 设置 | PLL2 设置 |

|--|----|---------|---------|

|  |    |         |         |

| 控制 Pin   | 输出状态选择 | 频率选择  | SSC 选择  | 输出状态选择 | 频率选择  | SSC 选择  | 输出状态选择 |

|----------|--------|-------|---------|--------|-------|---------|--------|

| S2 S1 S0 | Y1     | FS1   | SSC1    | Y2Y3   | FS2   | SSC2    | Y4Y5   |

| 0 0 0    | Y1_0   | FS1_0 | SSC1_0  | Y2Y3_0 | FS2_0 | SSC2_0  | Y4Y5_0 |

| 0 0 1    | Y1_1   | FS1_1 | SSC1_1  | Y2Y3_1 | FS2_1 | SSC2_1  | Y4Y5_1 |

| 0 1 0    | Y1_2   | FS1_2 | SSC1_2  | Y2Y3_2 | FS2_2 | SSC2_2  | Y4Y5_2 |

| 0 1 1    | Y1_3   | FS1_3 | SSC1_3  | Y2Y3_3 | FS2_3 | SSC2_3  | Y4Y5_3 |

| 1 0 0    | Y1_4   | FS1_4 | SSC1_4  | Y2Y3_4 | FS2_4 | SSC2_4  | Y4Y5_4 |

| 1 0 1    | Y1_5   | FS1_5 | SSC1_5  | Y2Y3_5 | FS2_5 | SSC2_5  | Y4Y5_5 |

| 1 1 0    | Y1_6   | FS1_6 | SSC1_6  | Y2Y3_6 | FS2_6 | SSC2_6  | Y4Y5_6 |

| 1 1 1    | Y1_7   | FS1_7 | SSC1_7  | Y2Y3_7 | FS2_7 | SSC2_7  | Y4Y5_7 |

| 寄存器地址    | 04h    | 0Ch   | 09h-0Bh | 0Eh    | 1Eh   | 1Bh-1Dh | 20h    |

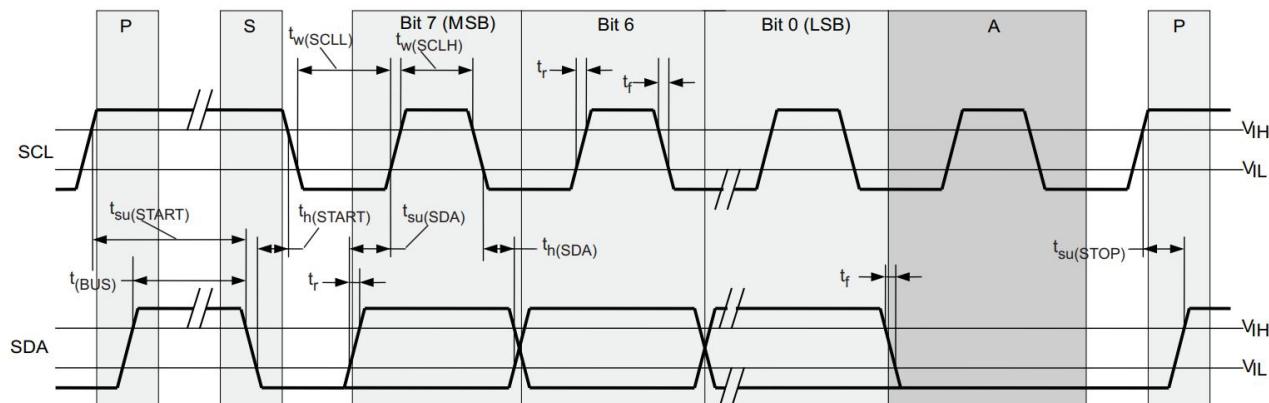

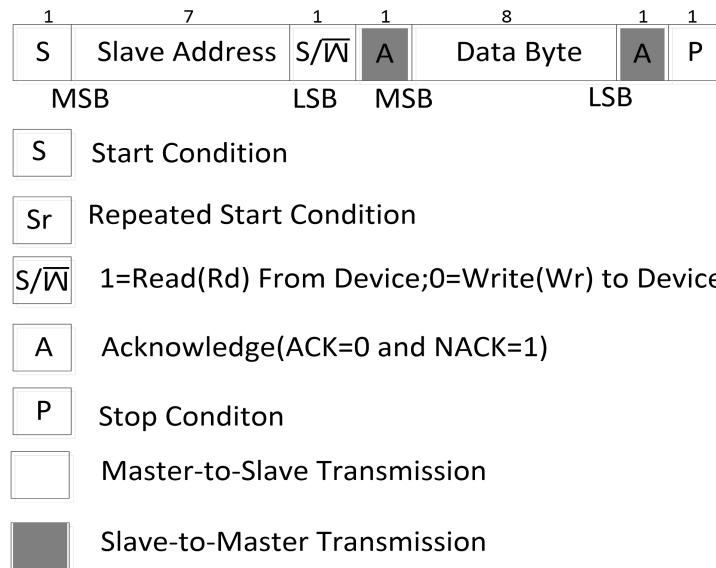

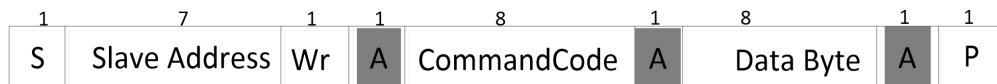

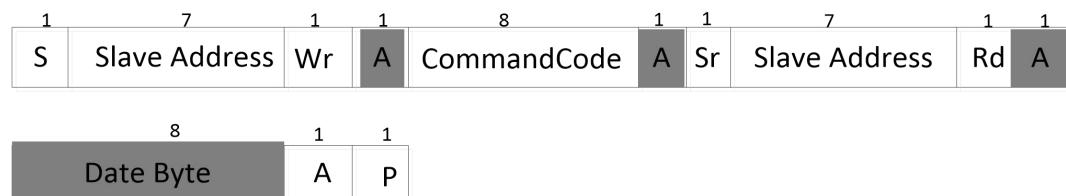

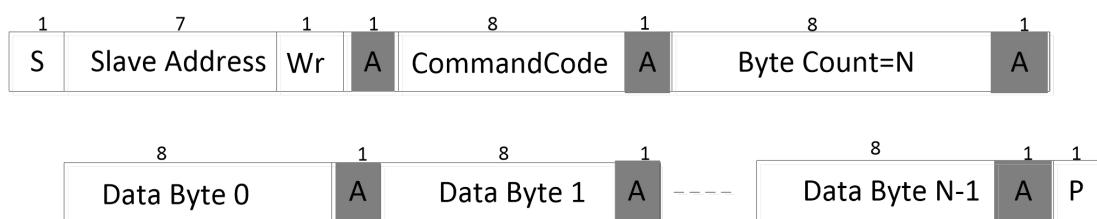

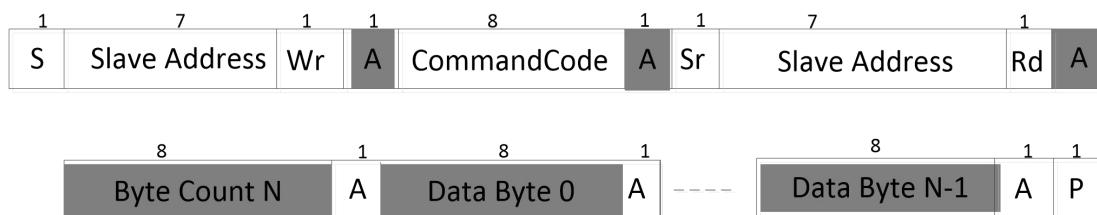

## 8.5 I2C

TLX925 支持 I2C 控制模式，采用两线制 SDA/SCL 的从机模式。支持标准传输模式（100kbps 速率）和快速模式（达 400kbps），7bit 位的寻址。

图 6 I2C 时序图

表 10 指令定义

| Bit   | 定义                                             |

|-------|------------------------------------------------|

| 7     | 0=Block 读或者 Block 写操作<br>1=Byte 读或者 Byte 写操作   |

| (6:0) | Byte 读, Block 读, Byte 写, Block 写模式时的 Byte 偏移地址 |

图 7 通用编程序列

图 8 字节写入协议

图 9 字节读协议

图 10 Block 写协议

图 11 Block 读协议

## 8.6 寄存器

表 11 寄存器列表

| 地址  | Bit 位 | 名称         | 默认值  | 作用                                                                                                            |

|-----|-------|------------|------|---------------------------------------------------------------------------------------------------------------|

| 00h | 7     | E_EL       | Xb   | 芯片定义 (只读)：<br>1 代表 CDCE925(3.3V 输出),<br>0 代表 CDCEL925 (1.8V 输出)                                               |

|     | 6:4   | RID        | Xb   | 标识号修订 (只读)                                                                                                    |

|     | 3:0   | VID        | 1h   | 产商标识 (只读)                                                                                                     |

| 01h | 7     | --         | 0b   | 保留, 一直为 0                                                                                                     |

|     | 6     | EEPIP      | 0b   | EEPROM 编程烧写状态 (只读)<br>0 代表程序烧写完成<br>1 代表程序烧写进行中                                                               |

|     | 5     | EELOCK     | 0b   | 永久锁定 EEPROM 中数据<br>0 表示未被锁定<br>1 表示永久锁定                                                                       |

|     | 4     | PWDN       | 0b   | 芯片关断 (覆盖 S0/S1/S2 设置; 配置寄存器的设置未改变, 注明: EEPROM 中 PWDN 不能设置为 1)。0 表示芯片工作 (所用的 PLL 和输出) 1 表示芯片关断 (PLL 不工作, 输出高阻) |

|     | 3:2   | INCLK<1:0> | 00b  | 输入时钟选择: 00-Xtal 01-VCXO 10-LVCMOS 11 保留, 未作定义                                                                 |

|     | 1:0   | SLAVE_ADR  | 00b  | 从接收器的地址位 A1 和 A0                                                                                              |

| 02h | 7     | M1         | 1b   | Y1 输出的时钟源选择: 0-输入时钟 1-PLL1 时钟                                                                                 |

|     | 6     | SPICON     | 0b   | PIN14/15 工作模式选择: 0-串行变成接口 SDA (PIN15) 和 SCL (PIN14) 1-控制引脚 S1 (PIN15) 和 S2 (PIN14)                            |

|     | 5:4   | Y1_ST1     | 11b  | Y1_State0/1 状态定义: 00-器件关断 (所有 PLL 关断, 所有输出高阻) ; 01-Y1 未使能, 处于高阻态; 10-Y1 处于低电平; 11-Y1 使能                       |

|     | 3:2   | Y1_ST0     | 01b  |                                                                                                               |

|     | 1:0   | Pdiv1[9:8] | 001h | Y1 输出 10bit 分频器                                                                                               |

| 03h | 7:0   | Pdiv1[7:0] |      | 0- 分频器复位和被旁路;<br>1 至 1023 为分频值                                                                                |

| 04h | 7     | Y1_7       | 0b   | Y1_ST0/Y1_ST1 状态选择: 0-State0(由 Y1_ST0 定义), 1-State1 (由 Y1_ST1 定义)                                             |

|     | 6     | Y1_6       | 0b   |                                                                                                               |

|     | 5     | Y1_5       | 0b   |                                                                                                               |

|     | 4     | Y1_4       | 0b   |                                                                                                               |

|     | 3     | Y1_3       | 0b   |                                                                                                               |

|     | 2     | Y1_2       | 0b   |                                                                                                               |

|     |       |             |      |                                                                                                                       |

|-----|-------|-------------|------|-----------------------------------------------------------------------------------------------------------------------|

|     | 1     | Y1_1        | 1b   |                                                                                                                       |

|     | 0     | Y1_0        | 0b   |                                                                                                                       |

| 05h | 7:3   | XCSEL       | 0Ah  | 晶振负载电容选择：00h-0pF<br>01h-1pF<br>02h-2pF<br>14 to 1Fh-20pF                                                              |

|     | <2:0> | --          | 0b   | 保留，一直为 0                                                                                                              |

| 06h | 7:1   | BCOUNT      | 30h  | 7bit 计数 ()                                                                                                            |

|     | 0     | EEWRITE     | 0b   | 初始化 EEPROM 写周期 0-EEPROM 没有初始化<br>1-开始 EEPROM 写周期                                                                      |

| 09h | 7:5   | SSC1_7[2:0] | 000b | SSC1: PLL1 SSC 功能选择 (调制深度)                                                                                            |

|     | 4:2   | SSC1_6[2:0] | 000b | Down Center<br>000(off) 000(off)                                                                                      |

|     | 1:0   | SSC1_5[2:1] | 000b | 001-0.25% 001±0.25%<br>010-0.5% 010±0.5%<br>011-0.75% 011±0.75%                                                       |

| 0Ah | 7     | SSC1_5[0]   | 000b | 100-1.0% 100±1%<br>101-1.25% 101±1.25%                                                                                |

|     | 6:4   | SSC1_4[2:0] | 000b | 110-1.5% 110±1.5%                                                                                                     |

|     | 3:1   | SSC1_3[2:0] | 000b |                                                                                                                       |

|     | 0     | SSC1_2[2]   | 000b | 111-2.0% 111±2%                                                                                                       |

| 0Bh | 7:6   | SSC1_2[1:0] | 000b |                                                                                                                       |

|     | 5:3   | SSC1_1[2:0] | 000b |                                                                                                                       |

|     | 2:0   | SSC1_0[2:0] | 000b |                                                                                                                       |

| 0Ch | 7     | FS1_7       | 0b   | FS1_x: PLL1 频率选择：<br>0-fvco1_0(由 PLL1_0 选通或者定义分频值)<br>1-fvco1_1(由 PLL1_1 选通定义分频值)                                     |

|     | 6     | FS1_6       | 0b   |                                                                                                                       |

|     | 5     | FS1_5       | 0b   |                                                                                                                       |

|     | 4     | FS1_4       | 0b   |                                                                                                                       |

|     | 3     | FS1_3       | 0b   |                                                                                                                       |

|     | 2     | FS1_2       | 0b   |                                                                                                                       |

|     | 1     | FS1_1       | 0b   |                                                                                                                       |

|     | 0     | FS1_0       | 0b   |                                                                                                                       |

| 0Dh | 7     | MUX1        | 1b   | PLL1 选择：0-PLL1 选通；<br>1-PLL1 关断，旁路                                                                                    |

|     | 6     | M2          | 1b   | Y2 输出选择：0-Pdiv1 1-Pdiv2                                                                                               |

|     | 5:4   | M3          | 10b  | Y3 输出选择：00-Pdiv1 分频值 01-Pdiv2 分频值 10-Pdiv3 分频值 11-保留                                                                  |

|     | 3:2   | Y2Y3_ST1    | 11b  | Y2, Y3-state0/1 定义：00-Y2/Y3 高阻态 (PLL1 关断)<br>01-Y2/Y3 高阻态 (PLL1 工作) 10-Y2/Y3 低电平 (PLL1 工作)<br>11-Y2/Y3 正常输出 (PLL1 工作) |

|     | 1:0   | Y2Y3_ST0    | 01b  |                                                                                                                       |

|     | 7     | Y2Y3_7      | 0b   | Y2Y3_x_output 状态选择<br>0-state0(由 Y2Y3_ST0 定义)<br>1-state1(由 Y2Y3_ST1 定义)                                              |

|     | 6     | Y2Y3_6      | 0b   |                                                                                                                       |

|     | 5     | Y2Y3_5      | 0b   |                                                                                                                       |

|     |     |                   |                     |                                                                                                        |  |

|-----|-----|-------------------|---------------------|--------------------------------------------------------------------------------------------------------|--|

| 0Eh | 4   | Y2Y3_4            | 0b                  |                                                                                                        |  |

|     | 3   | Y2Y3_3            | 0b                  |                                                                                                        |  |

|     | 2   | Y2Y3_2            | 0b                  |                                                                                                        |  |

|     | 1   | Y2Y3_1            | 1b                  |                                                                                                        |  |

|     | 0   | Y2Y3_0            | 0b                  |                                                                                                        |  |

| 0Fh | 7   | SSC1DC            | 0b                  | PLL1 SSC 下/中心扩频选择:<br>0-下<br>1-中心                                                                      |  |

|     | 6:0 | Pdiv2             | 01h                 | 7bit Y2 输出分频器 Pdiv2 设置:0-复位并被旁路<br>1 到 127 分频值                                                         |  |

| 10h | 7:1 | Pdiv3             | 01h                 | 7bit Y3 输出分频器 Pdiv3 设置: 0-复位并被旁路<br>1 到 127 分频值可调                                                      |  |

|     | 0   | PLL1_N[11]        | 0b                  | PLL1_DIV_N<11:0>是 PLL1 中的环路中的反馈分频数控<br>制字                                                              |  |

| 11h | 7:0 | PLL1_N[10:3]      | 014h                |                                                                                                        |  |

| 12h | 7:5 | PLL1_N[2:0]       |                     |                                                                                                        |  |

|     | 4:0 | PLL1_M[8:4]       | 005h                | PLL1_DIV_M<8:0>是 PLL1 中参考频率预分频控制字                                                                      |  |

| 13h | 7:4 | PLL1_M[3:0]       |                     |                                                                                                        |  |

|     | 3   | PDIV_EN           | 1b                  | 输出通道分频器的使能控制                                                                                           |  |

|     | 2:1 | --                | 11b                 | 保留,一直为 11b                                                                                             |  |

|     | 0   | VCO1_0_RANGE<1>   | 00b                 | Fvco1_0 输出范围选择: 00-fvco1_0<125M 01-<br>125M<=fvco1_0<150M<br>10-150M<=fvco1_0<175M<br>11-Fvco1_0>=175M |  |

| 14h | 7   | VCO1_0_RANGE<0>   |                     |                                                                                                        |  |

|     | 6:5 | VCO1_1_RANGE<1:0> | 00b                 | Fvco1_1 输出范围选择: 00-fvco1_1<125M<br>01-125M<=fvco1_1<150M<br>10-150M<=fvco1_1<175M<br>11-Fvco1_1>=175M  |  |

|     | 4:0 | --                | 01100b              |                                                                                                        |  |

| 1Bh | 7:5 | SSC2_7[2:0]       | 000b                | SSC2: PLL2 SSC 功能选择 (调制深度)<br>Down Center<br>000(off) 000(off)                                         |  |

|     | 4:2 | SSC2_6[2:0]       | 000b                |                                                                                                        |  |

|     | 1:0 | SSC2_5[2:1]       | 000b                |                                                                                                        |  |

| 1Ch | 7   | SSC2_5[0]         | 001-0.25% 001±0.25% |                                                                                                        |  |

|     | 6:4 | SSC2_4[2:0]       | 000b                | 010-0.5% 010±0.5%                                                                                      |  |

|     | 3:1 | SSC2_3[2:0]       | 000b                | 011-0.75% 011±0.75%                                                                                    |  |

|     | 0   | SSC2_2[2]         | 000b                | 100-1.0% 100±1%                                                                                        |  |

| 1Dh | 7:6 | SSC2_2[1:0]       |                     | 101-1.25% 101±1.25%                                                                                    |  |

|     | 5:3 | SSC2_1[2:0]       | 000b                | 110-1.5% 110±1.5%                                                                                      |  |

|     | 2:0 | SSC2_0[2:0]       | 000b                | 111-2.0% 111±2%                                                                                        |  |

| 1Eh | 7   | FS2_7             | 0b                  | FS2_x: PLL2 频率选择:                                                                                      |  |

|     |     |                   |        |                                                                                                        |

|-----|-----|-------------------|--------|--------------------------------------------------------------------------------------------------------|

|     | 6   | FS2_6             | 0b     | 0-Fvco2_0(由 PLL2_0 选通或者定义分频值)<br>1-fvco2_1(由 PLL2_1 选通定义分频值)                                           |

|     | 5   | FS2_5             | 0b     |                                                                                                        |

|     | 4   | FS2_4             | 0b     |                                                                                                        |

|     | 3   | FS2_3             | 0b     |                                                                                                        |

|     | 2   | FS2_2             | 0b     |                                                                                                        |

|     | 1   | FS2_1             | 0b     |                                                                                                        |

|     | 0   | FS2_0             | 0b     |                                                                                                        |

| 20h | 7   | Y4Y5_7            | 0b     | Y4Y5_x 输出状态选择<br>0-state0(由 Y4Y5_ST0 定义)<br>1-State1(由 Y4Y5_ST1 定义)                                    |

|     | 6   | Y4Y5_6            | 0b     |                                                                                                        |

|     | 5   | Y4Y5_5            | 0b     |                                                                                                        |

|     | 4   | Y4Y5_4            | 0b     |                                                                                                        |

|     | 3   | Y4Y5_3            | 0b     |                                                                                                        |

|     | 2   | Y4Y5_2            | 0b     |                                                                                                        |

|     | 1   | Y4Y5_1            | 1b     |                                                                                                        |

|     | 0   | Y4Y5_0            | 0b     |                                                                                                        |

| 21h | 7   | SSC2DC            | 0b     | PLL2 SSC 下/中心扩频选择：<br>0-下<br>1-中心                                                                      |

|     | 6:0 | Pdiv4             | 01h    | Y4 7bit Pdiv4 输出分频器:0-复位和旁路<br>1 到 127 分频                                                              |

| 22h | 7   | -                 | 1b     | 保留, 一直为 1                                                                                              |

|     | 6:0 | Pdiv5             | 01h    | Y5 7bit 分频器输出: 0-复位和旁路<br>1 到 127 分频                                                                   |

| 23h | 7:0 | PLL2_N[7:0]       | 014h   | PLL2_DIV_N<11:0>是 PLL2 中的环路中的反馈分频数控制字                                                                  |

| 24h | 7:4 | PLL2_N[11:8]      |        |                                                                                                        |

|     | 3:0 | PLL2_M[8:5]       | 005h   | PLL2_DIV_M<8:0>是 PLL2 中参考频率预分频控制字                                                                      |

| 25h | 7:3 | PLL2_M4:0]        |        |                                                                                                        |

|     | 2:1 |                   |        |                                                                                                        |

|     | 0   |                   |        |                                                                                                        |

| 26h | 7   | VCO2_0_RANGE<1:0> | 00b    | Fvco2_0 输出范围选择: 00-fvco2_0<125M 01-<br>125M<=fvco2_0<150M<br>10-150M<=fvco2_0<175M<br>11-fvco2_0>=175M |

|     | 6:5 | VCO2_1_RANGE<1:0> | 00b    | Fvco2_1 输出范围选择: 00-fvco2_1<125M 01-<br>125M<=fvco2_1<150M<br>10-150M<=fvco2_1<175M<br>11-fvco2_1>=175M |

|     | 4:0 | ---               | 01100b | 保留, 一直为 01100b                                                                                         |

| 2Eh | 7:0 | check_code        | 00h    | 烧写前, 此寄存器必须先写 55h。                                                                                     |

| 36h | 7   | MUX2              | 1b     | PLL2 选通: 0-PLL2                                                                                        |

|     |          |           |   |                                                                                                                              |

|-----|----------|-----------|---|------------------------------------------------------------------------------------------------------------------------------|

|     |          |           |   | 1- PLL2 旁路 (PLL2 关断)                                                                                                         |

| 6   | M4       | 1b        |   | Y4 选通: 0-Pdiv2 输出<br>1-Pdiv4 输出                                                                                              |

| 5:4 | M5       | 10b       |   | Y5 选通 00-Pdiv2 分频输出<br>01-Pdiv4 分频输出<br>10-Pdiv5 分频输出<br>11-保留                                                               |

| 3:2 | Y4Y5_ST1 | 11b       |   | Y4,Y5-State0/1 定义:<br>00-Y4/Y5 高阻态 (PLL2 关断) 01-Y4/Y5 高阻态 (PLL2 工作)<br>10-Y4/Y5 低电平 (PLL2 工作)<br>11-Y4/Y5 使能 (正常工作, PLL2 工作) |

| 1:0 | Y4Y5_ST0 | 01b       |   |                                                                                                                              |

| 37h | <7:6>    | --        | 0 | 保留, 一直为 0                                                                                                                    |

|     | 5: 0     | EE_UNLOCK |   | 当 EEPROM 锁住之后的后门解锁, 当为 6' b101010 时, 解锁。                                                                                     |

## 9 应用细节

### 9.1 通道输出频率设置

PLL 通道输出频率满足以下公式:

$$f_{out} = \frac{f_{in}}{Pdiv} \frac{N}{M}$$

其中,  $f_{in}$  为晶振振荡频率或者是外部输入频率,  $N$  为 PLL 的反馈分频比, 可以通过  $PLL\_N$  设置,  $M$  为 PLL 的预分频比, 可以通过  $PLL\_M$  设置。Pdiv 为通道对应的分频器。

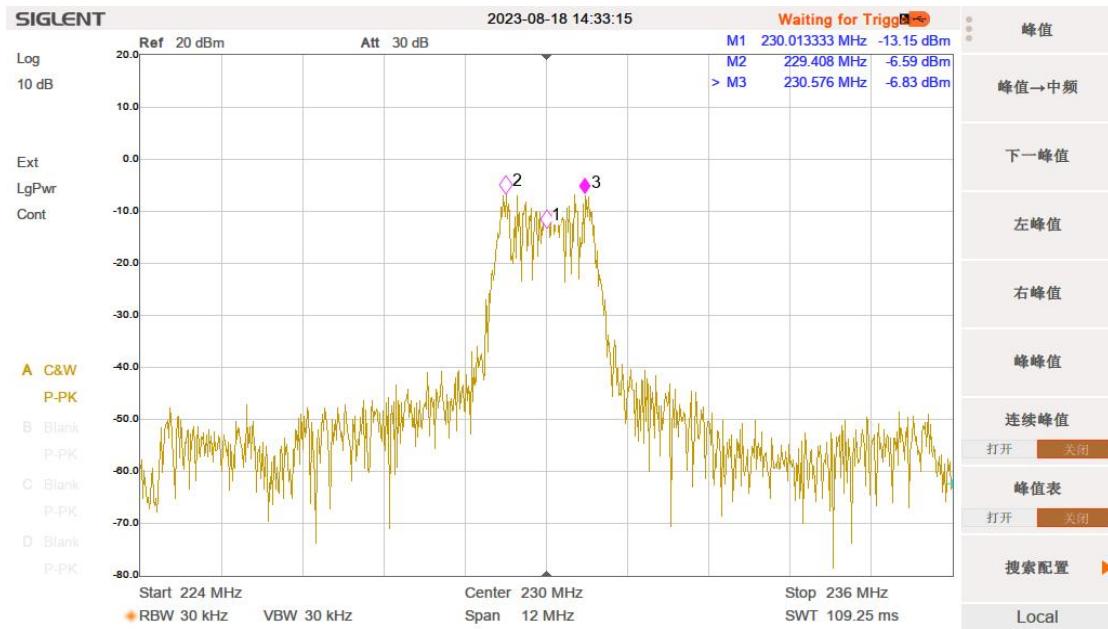

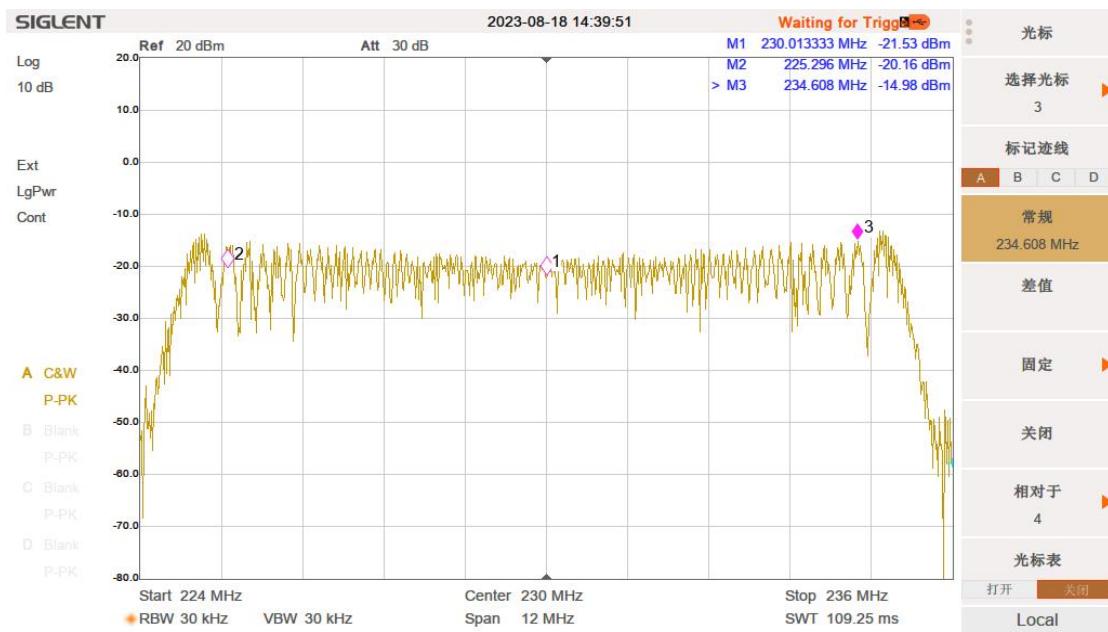

## 9.2 时钟扩频 (SSC)

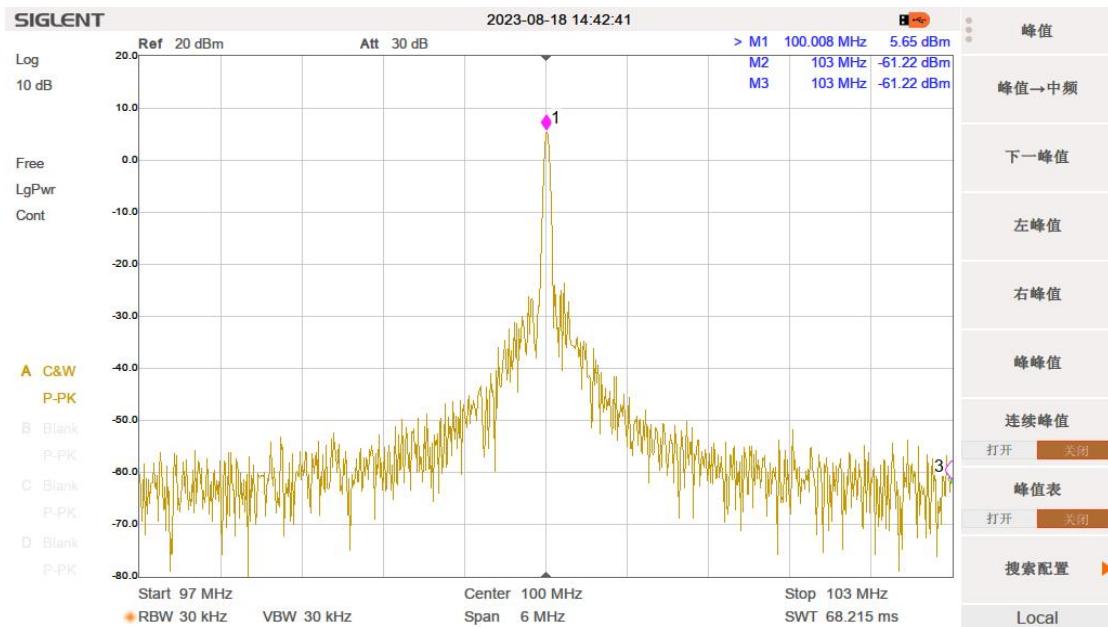

图 12 100M no SSC

图 13 100M ±0.25%中心扩频

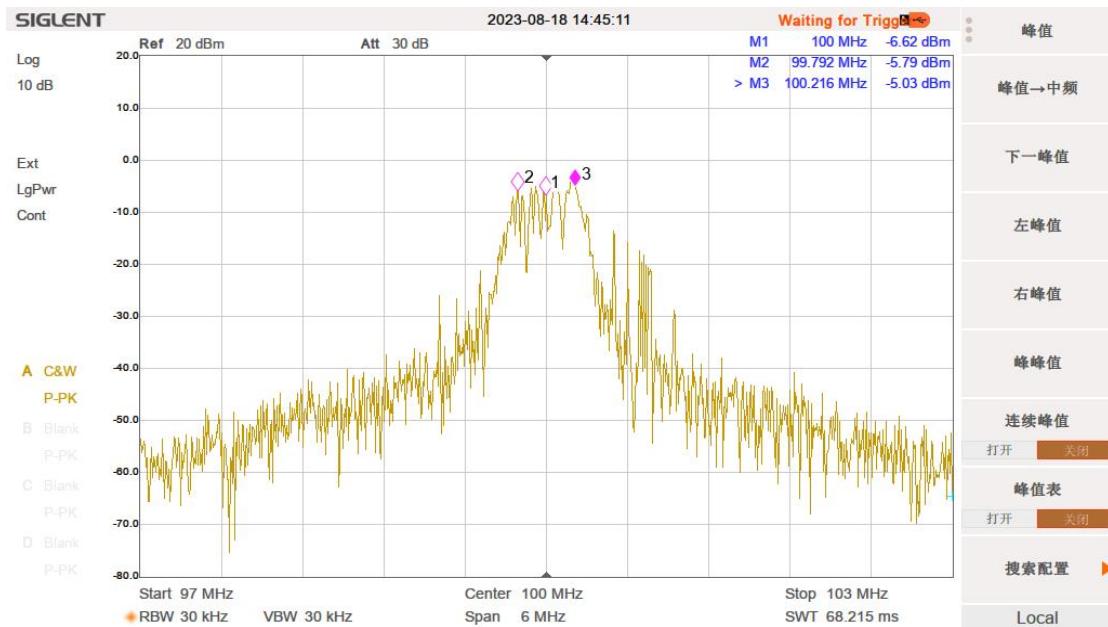

图 14 100M ±2%中心扩频

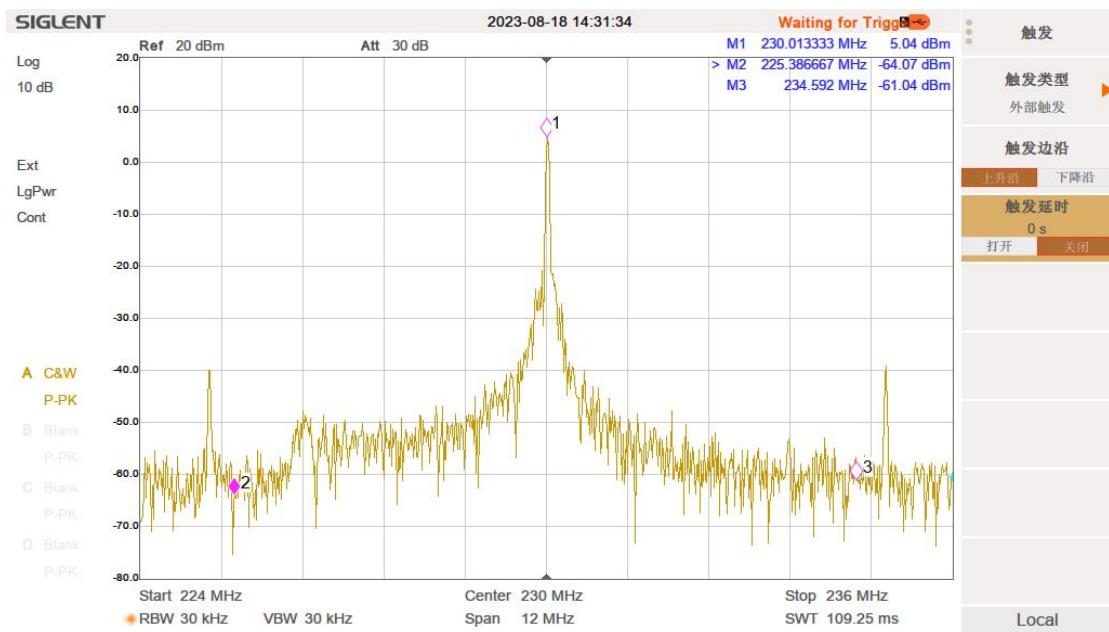

图 15 230M no SSC

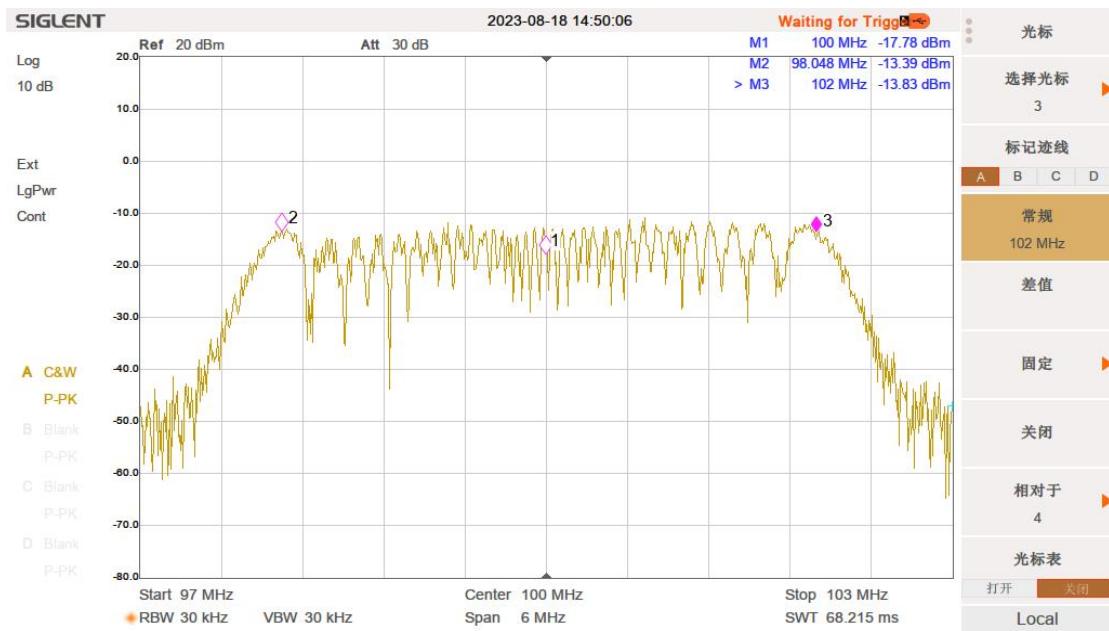

图 16 230M  $\pm 0.25\%$  中心扩频图 17 230M  $\pm 2\%$  中心扩频

## 10 外形尺寸

图 18 TSSOP16 封装尺寸图

## 订购信息

| 订购型号    | 温度等级            | 封装类型    | 丝印 <sup>(2)</sup> | MSL    | 质量等级   |

|---------|-----------------|---------|-------------------|--------|--------|

| JTLX925 | -55 °C ~+125 °C | TSSOP16 | JTLX925           | MSL1/3 | N1/军温级 |

| TLX925  | -40 °C ~+125 °C | TSSOP16 | TLX925            | MSL1/3 | 工业级    |